Memory Map

16 MIPS® Malta™ User’s Manual, Revision 01.07

Copyright © 2000-2007 MIPS Technologies Inc. All rights reserved.

3.4 Switches / Status

The SWITCH, STATUS, and JPMRS registers allow software to monitor the state of various switches and jumpers

on the Malta Board. All DIP switches have a value of “1” for a switch in the “ON” position.

A switch is considered ON if any of the following are true:

• It is in the position marked “ON” on the switch body.

• It is in the position marked “CLOSED” or not in the “OPEN” position as marked on the switch body.

There is no debouncing on these registers, so if software wants to monitor a value while it changes, allowance for this

must be made by waiting for the new value to become stable.

For the DIP switches S2 & S5, bit 0 is marked by a dot or by a “0” in the silkscreen, or the switch is marked by a “1”.

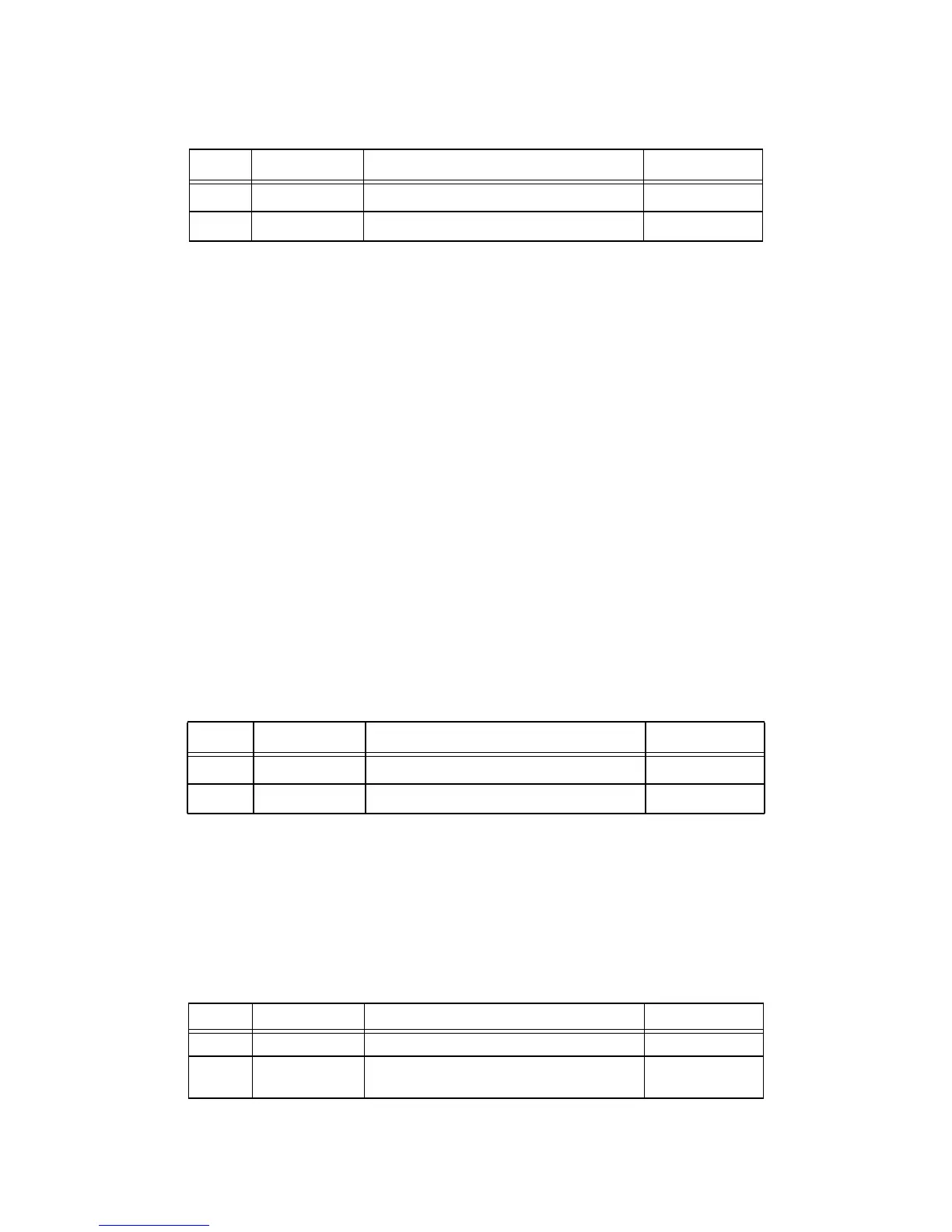

Table 3.5 NMIACK Register

Bits Field Name Function Initial Value

31:1 Reserved Reserved n/a

0 ONNMI Write 1 to acknowledge ON/NMI NMI n/a

Name: SWITCH

Address: 0x1F00.0200

Access: RO

Reset Value: n/a

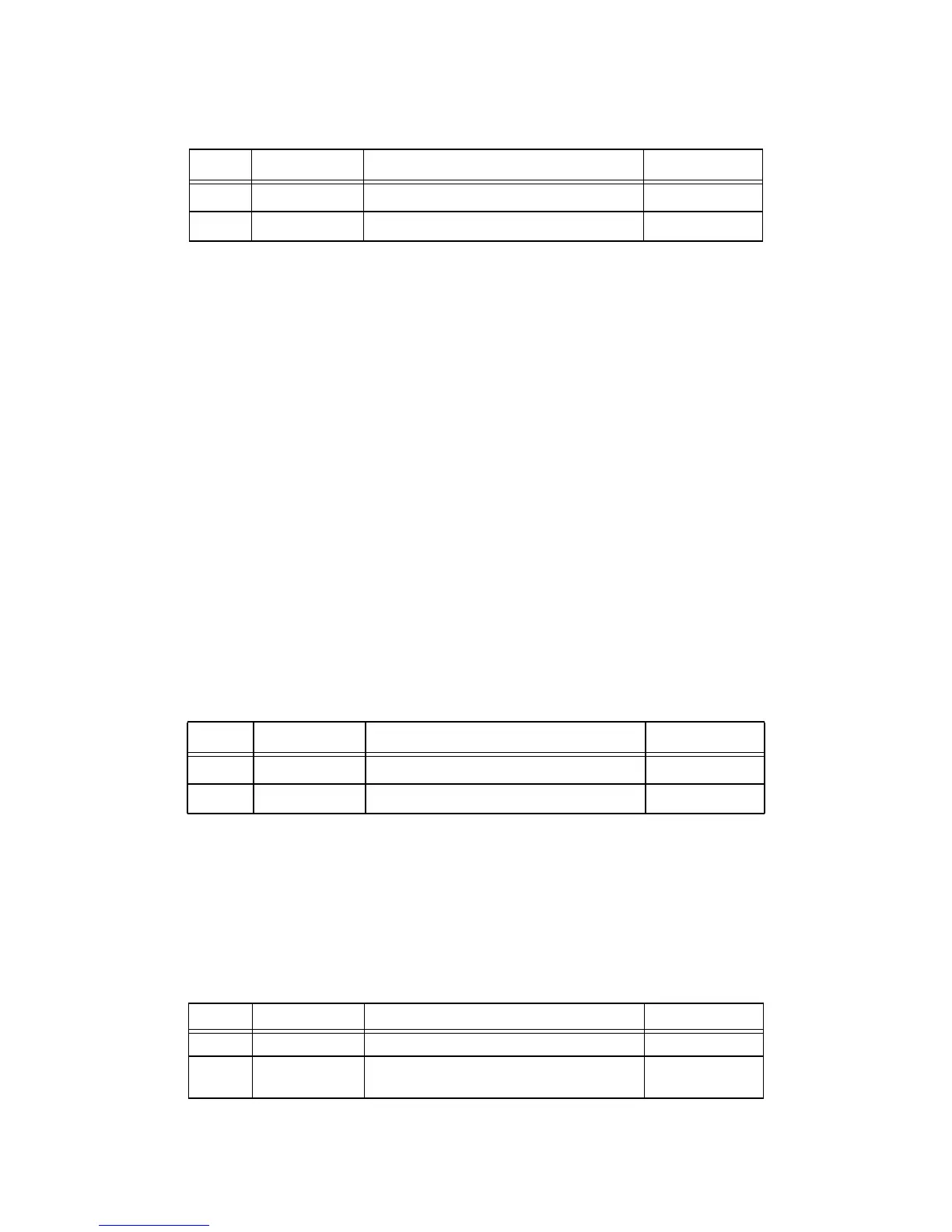

Table 3.6 SWITCH Register

Bits Field Name Function Initial Value

31:8 Reserved Reserved 0

7:0 S2 8-bit value of the setting of DIP switch S2. n/a

Name: STATUS

Address: 0x1F00.0208

Access: RO

Reset Value: n/a

Table 3.7 STATUS Register

Bits Field Name Function Initial Value

31:5 Reserved Reserved 0

4 MFWR “1” indicates Monitor Flash lock bits are write

protected (JP1 fitted).

n/a

Loading...

Loading...