5.6 Interrupt Controller

MIPS® Malta™ User’s Manual, Revision 01.07 35

Copyright © 2000-2007 MIPS Technologies Inc. All rights reserved.

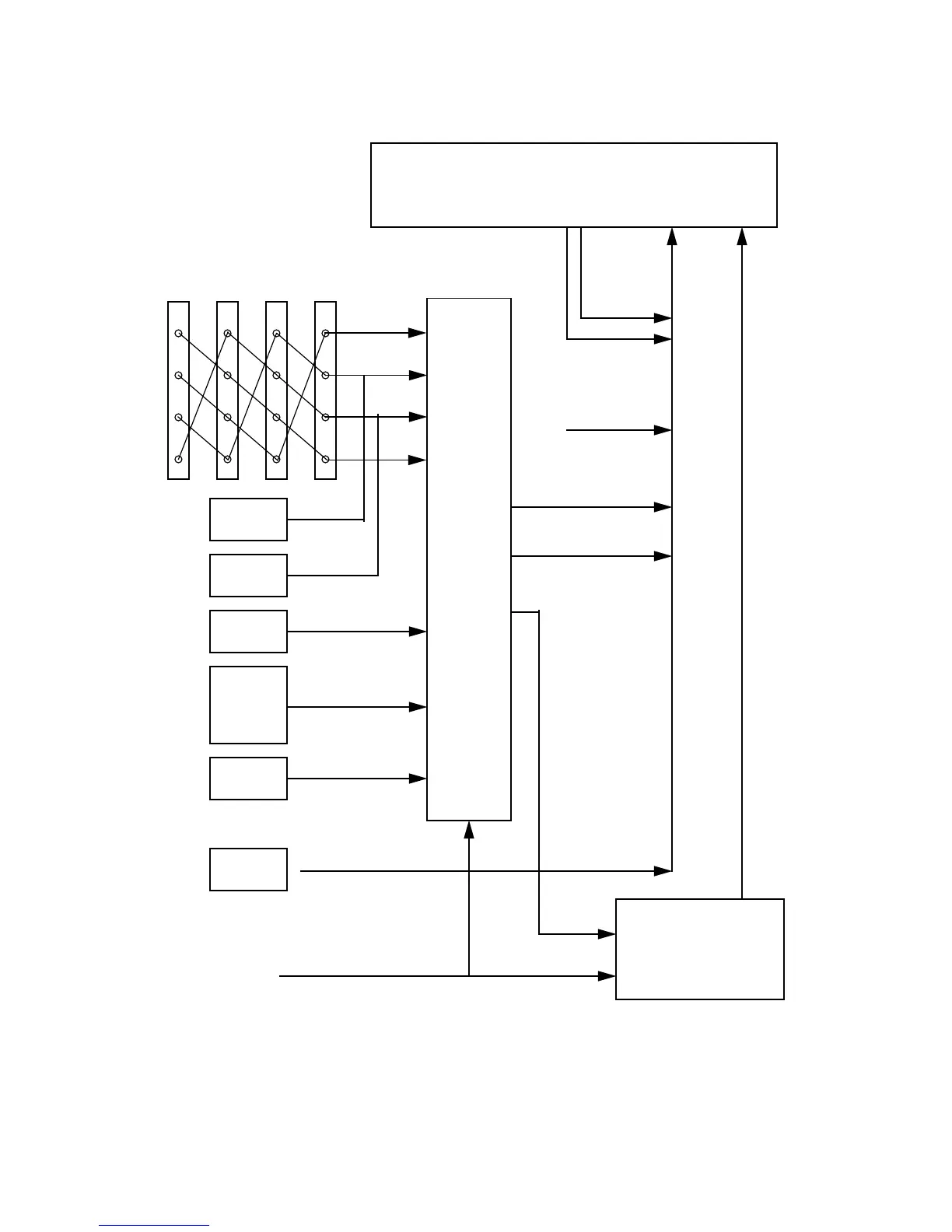

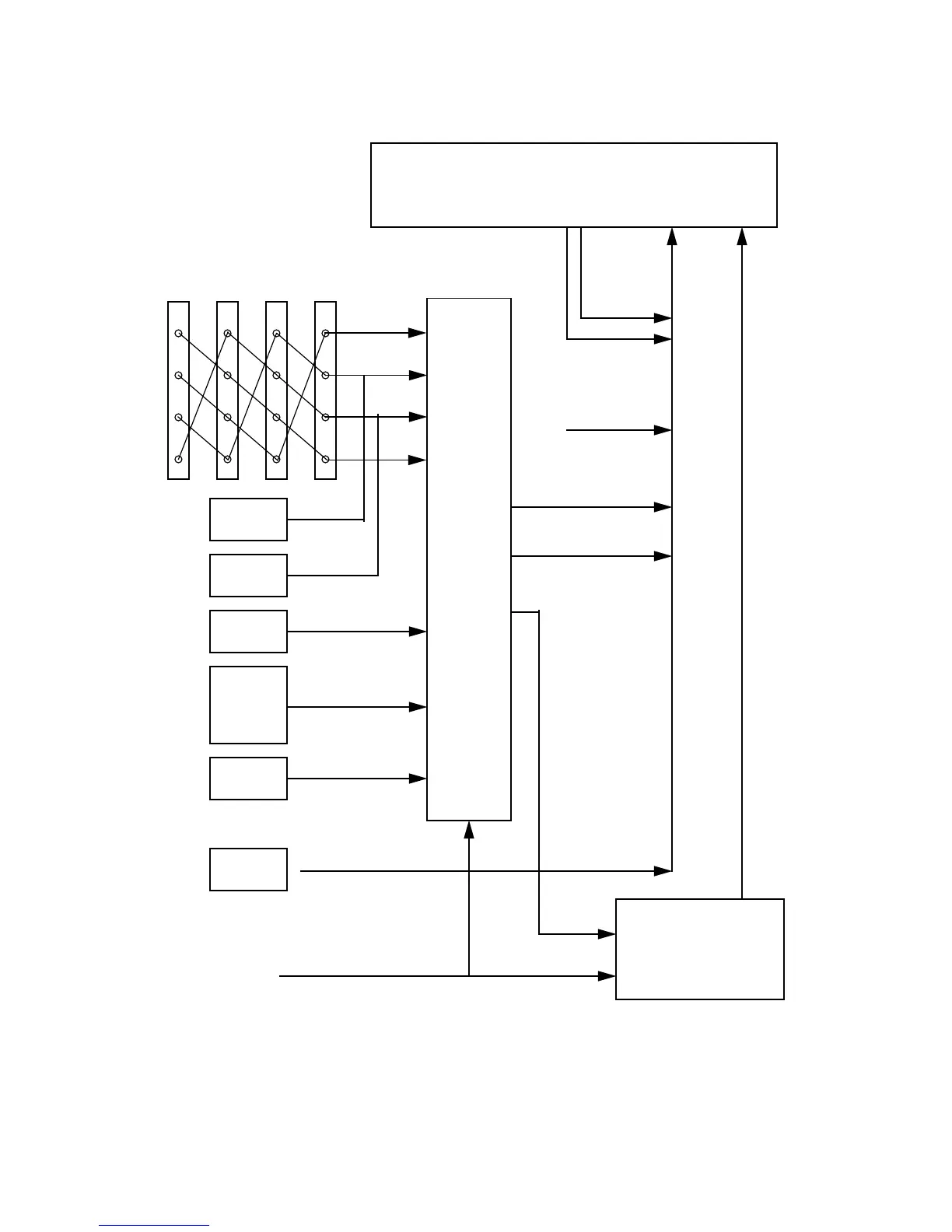

Figure 5.2 Interrupt Wiring

Most sources of interrupt are handled in an interrupt controller located in the South Bridge. A few are handled in the

CBUS FPGA (COREHI, CORELO and CBUS UART (tty2) interrupt), this means that CPU and CBUS interrupt

sources can be handled before the PCI bus has been configured. Please use the macros in the header file to access all

registers and fields of the interrupt controller, as described in [3].

A

B

C

D

A

B

C

D

A

B

C

D

A

B

C

D

Serial IRQ

tty2

INTR

SMI

COREHI

CORELO

NMI

NMI

ON/NMI

INT 0..5

CORE Card

South

SuperI/O

NMI Controller

PCI A

PCI B

PCI C

PCI D

Ethernet

Audio

IRQ 14

IRQ 15

Prim. IDE

connector

Sec. IDE/

Compact

PCI slots 4..1

PwrBtn

Bridge

Flash

connector

INT 1

INT 3

INT 4

INT 2

INT 0

INT 5

deasserted

Loading...

Loading...