Hardware Description

32 MIPS® Malta™ User’s Manual, Revision 01.07

Copyright © 2000-2007 MIPS Technologies Inc. All rights reserved.

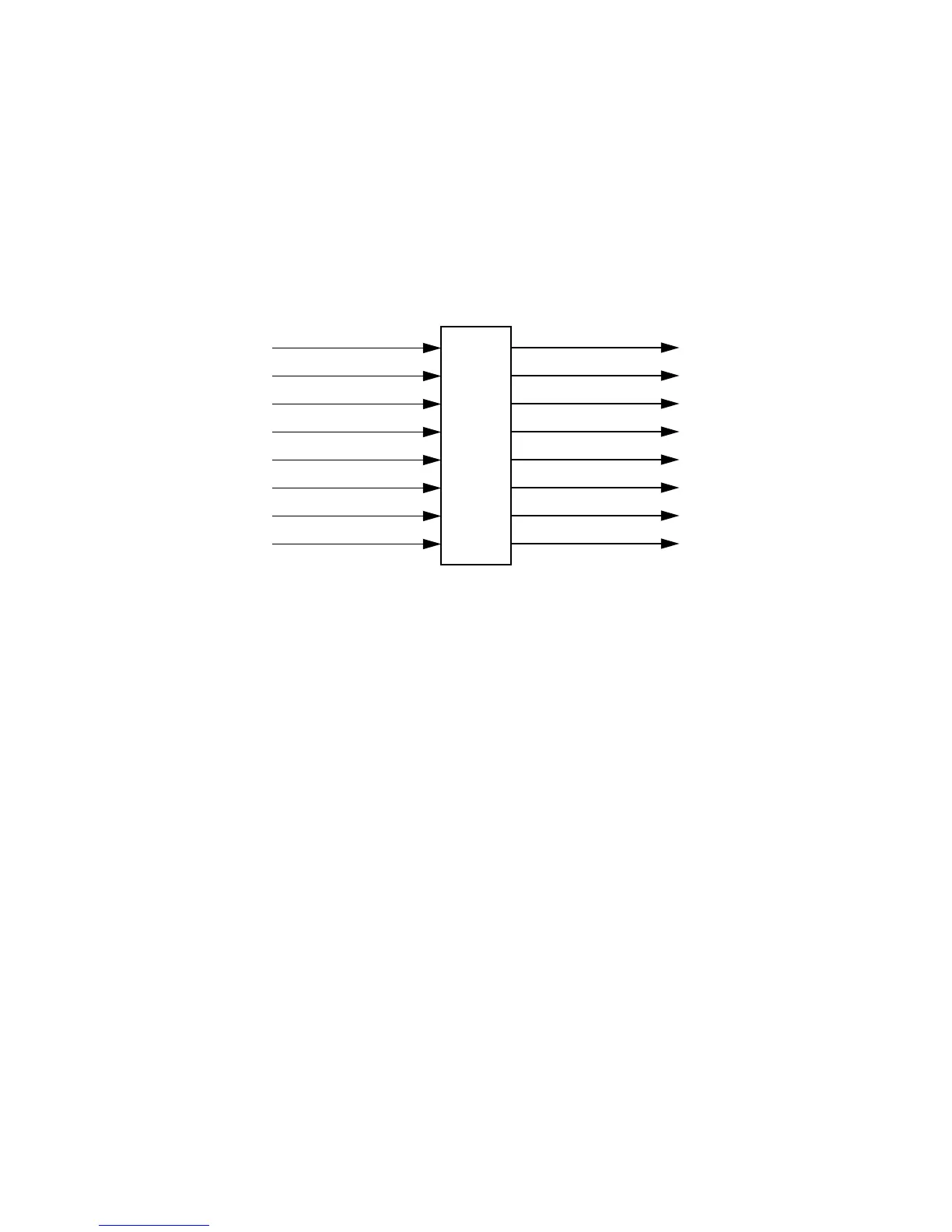

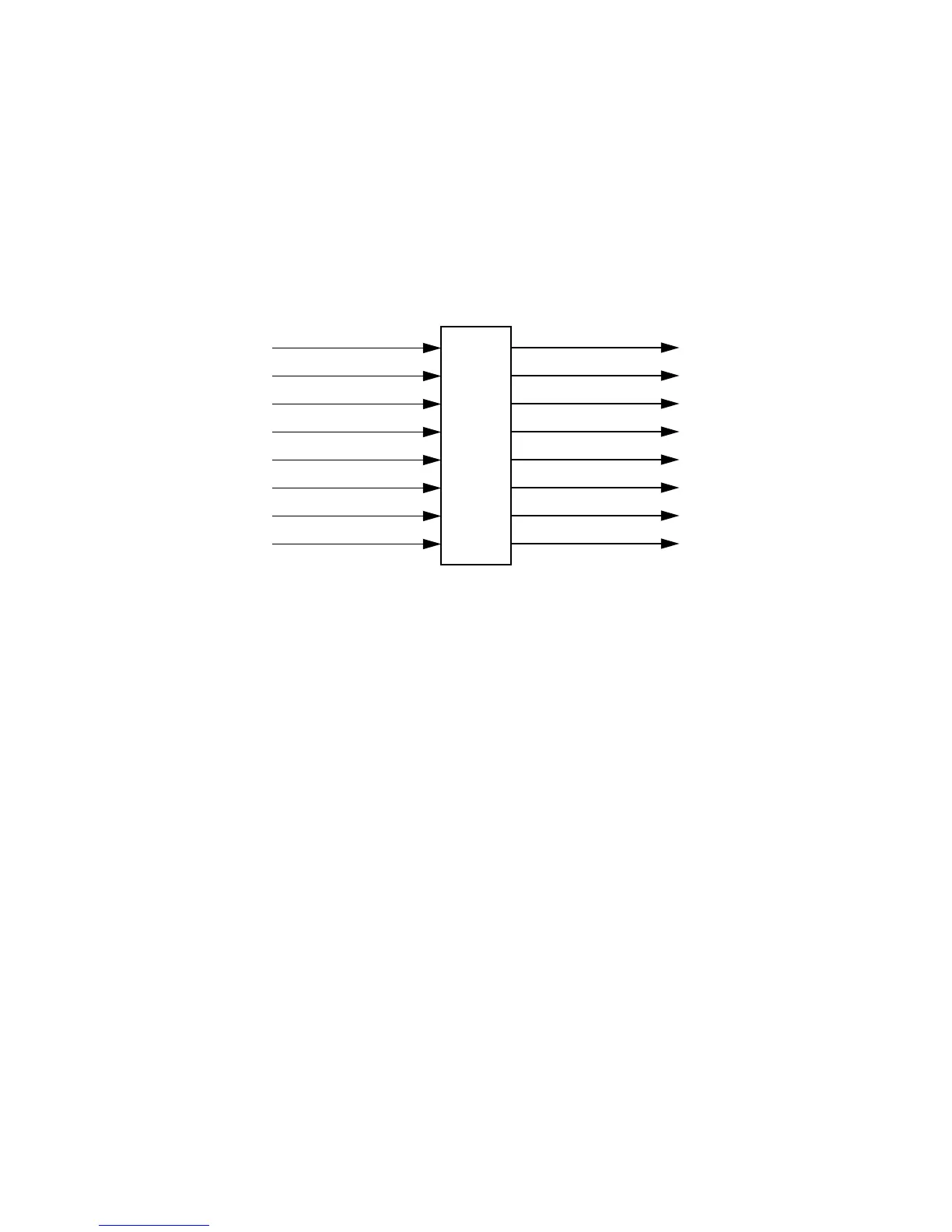

5.1.1 PCI Arbiter

The PCI arbiter controls the request and grant scheduling to the eight PCI components and is implemented in an

Altera MAX3064 EPLD.

The PCI arbiter implements a round-robin scheme, where each of the eight components have equal priority.

Figure 5.1 shows the signals used during PCI arbitration.

Figure 5.1 PCI Arbiter Connections

5.2 I

2

C Bus

The Malta Board has two I

2

C controllers:

• a simple one in the FPGA, used for accessing SDRAM information for debug purposes and similar operations

when the PCI bus is unconfigured

• a more advanced controller in the South Bridge used for normal operation

The active I

2

C controller is set in the I2CSEL register in FPGA.

5.3 Power

The board operates with 3.3V and 5V, supplied from a standard PC ATX power supply connected to J8. This should

be able to supply enough current for the board and all conceivable Core Board options. The 12V and -12V is only

connected to the Core Board (only 12V) and the AMR and PCI connectors. See [11] for details of a suitable supply.

Power On/Off is controlled by the South Bridge and its function is similar to a PC.

The board also supports Power Management Events, for eample, Wake On LAN events, used for powering up in

stand-by mode.

PCI

Arbiter

pci_gnt#_corepci_req#_core

pci_gnt#_southbridgepci_req#_southbridge

pci_gnt#_ethernetpci_req#_ethernet

pci_gnt#_audiopci_req#_audio

pci_gnt#_con1pci_req#_con1

pci_gnt#_con2pci_req#_con2

pci_gnt#_con3pci_req#_con3

pci_gnt#_con4pci_req#_con4

Loading...

Loading...