5.17 Debug Access

MIPS® Malta™ User’s Manual, Revision 01.07 41

Copyright © 2000-2007 MIPS Technologies Inc. All rights reserved.

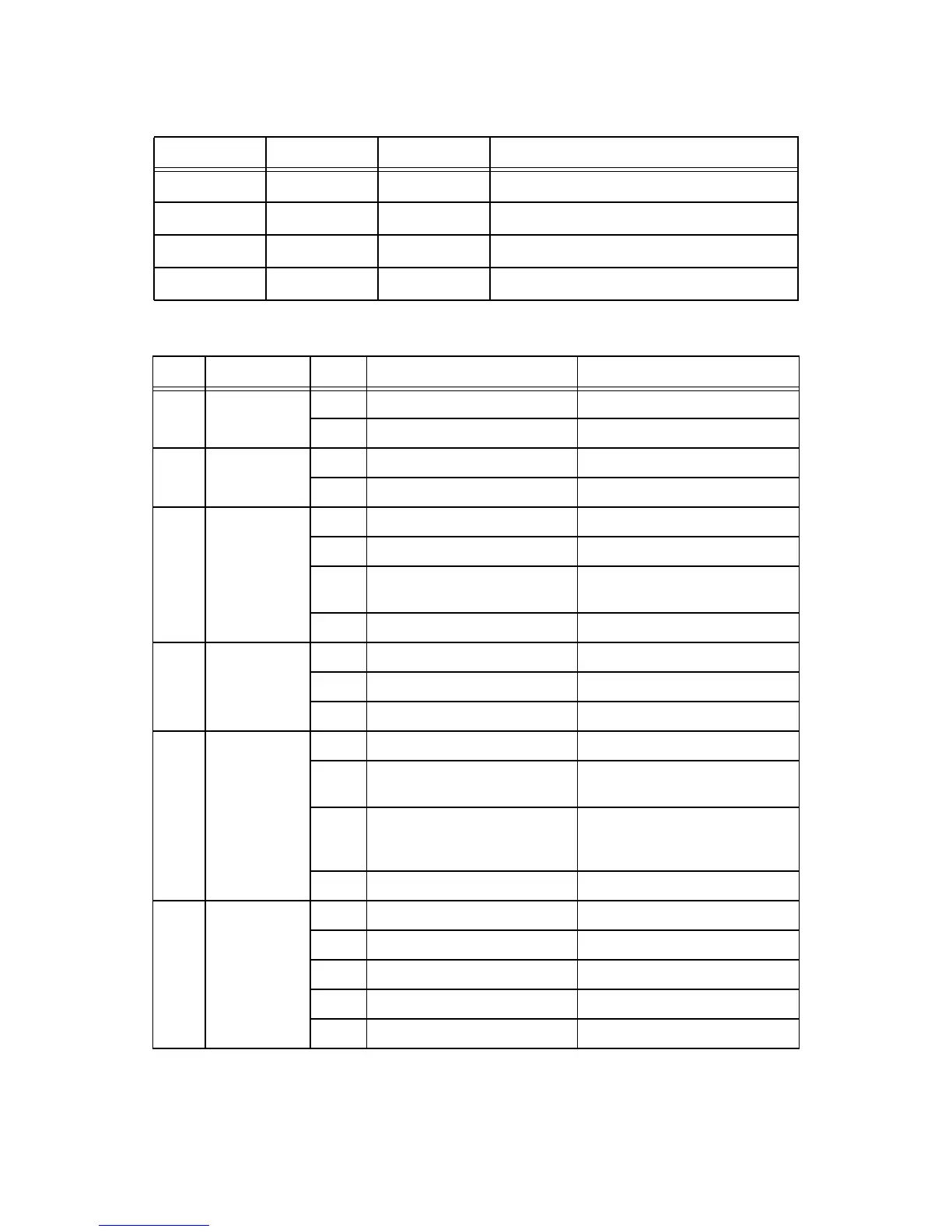

TP4 D5V Red Digital 5V rail

TP5 D12V Red Digital 12V rail

TP6 D12VN Red Digital -12V rail

TP7-12 GND Black Ground

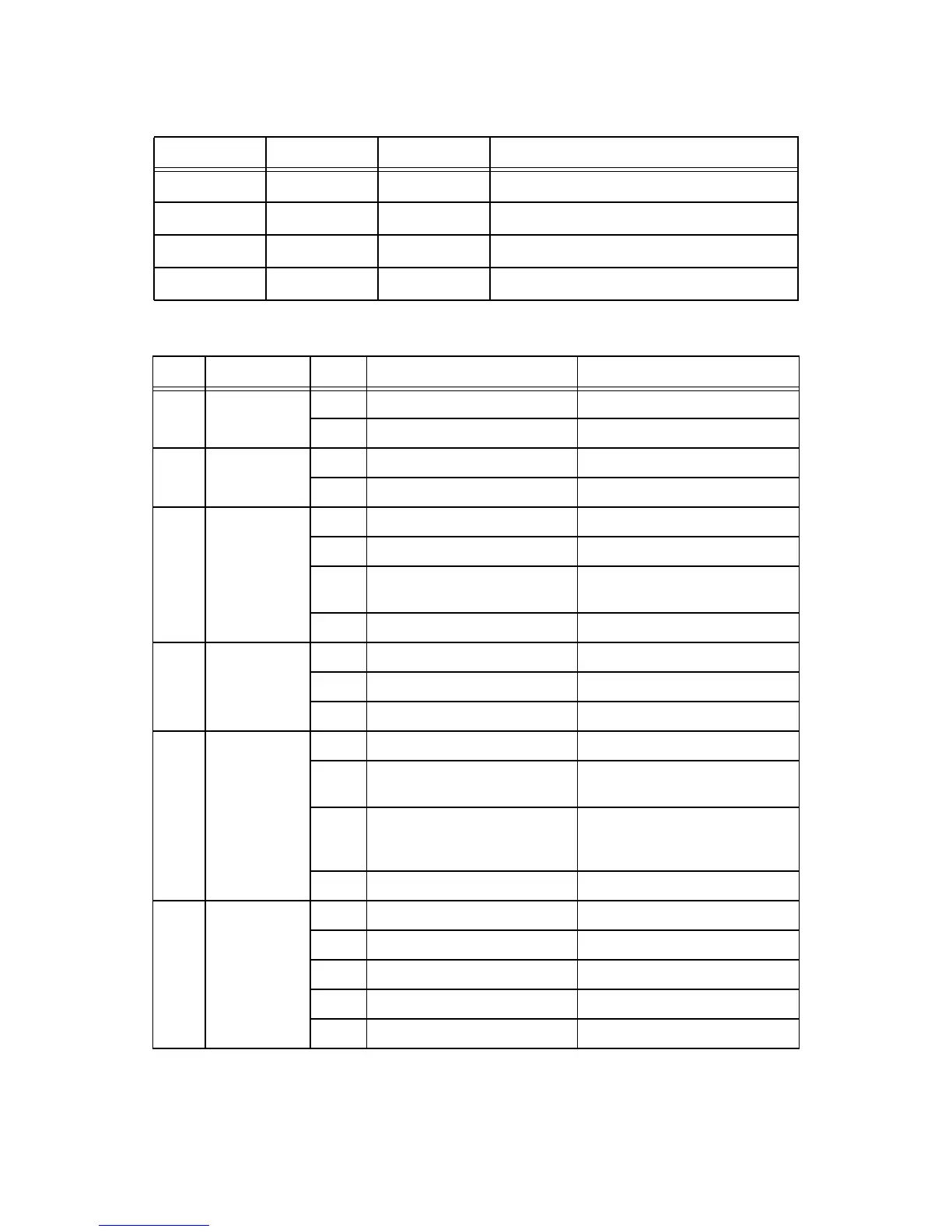

Table 5.6 Logic Analyser Connectors

Ref Function Bits Signals Description

J23

Even

CBUS DATA Clock CLK_40MHZ 40 MHz

15:0 CBUS_D[31:16] CBUS data

J23

Odd

CBUS DATA Clock PCI_CLK 33.33 MHz (default)

15:0 CBUS_D[15:0] CBUS data

J24

Even

CBUS Clock CLK_1KHZ 1 KHz

15:13 FPGA_RSTN, RSTN, BIGEND CBUS FPGA signals

12:10 CBUS_WRN, CBUS_RDN,

CBUS_CSN

CBUS control

9:0 CBUS_A[25:16] CBUS address

J24

Odd

CBUS ADDR Clock CLK_32KHZ 32 KHz

15:2 CA[15:2] CBUS address

1:0 GND Used as CA[1:0]

J25

Even

CBUS FPGA Clock CLK_40MHZ 40 MHz

15:12 FRSTN, PAR_ENAB,

FPGA_RSTN, MFSTS

11:4 UCSN, REVCSN, CGPIOCSN,

CGPIOWR, MFCSN, ASWCSN,

ADCSN, ABRLEDCS

Chip selects

3:0 Not used

J25

Odd

IIC + ASCII

Display

Clock PCI_CLK 33.33 MHz (default)

15:14 IIC_SCL, IIC_SDA IIC signals

13 Not Used

12:8 ADA[4:0] ASCII display address

7:0 ADD[7:0] ASCII display data

Table 5.5 Testpoints (Continued)

Ref Silkscreen Color Function

Loading...

Loading...