Hardware Description

42 MIPS® Malta™ User’s Manual, Revision 01.07

Copyright © 2000-2007 MIPS Technologies Inc. All rights reserved.

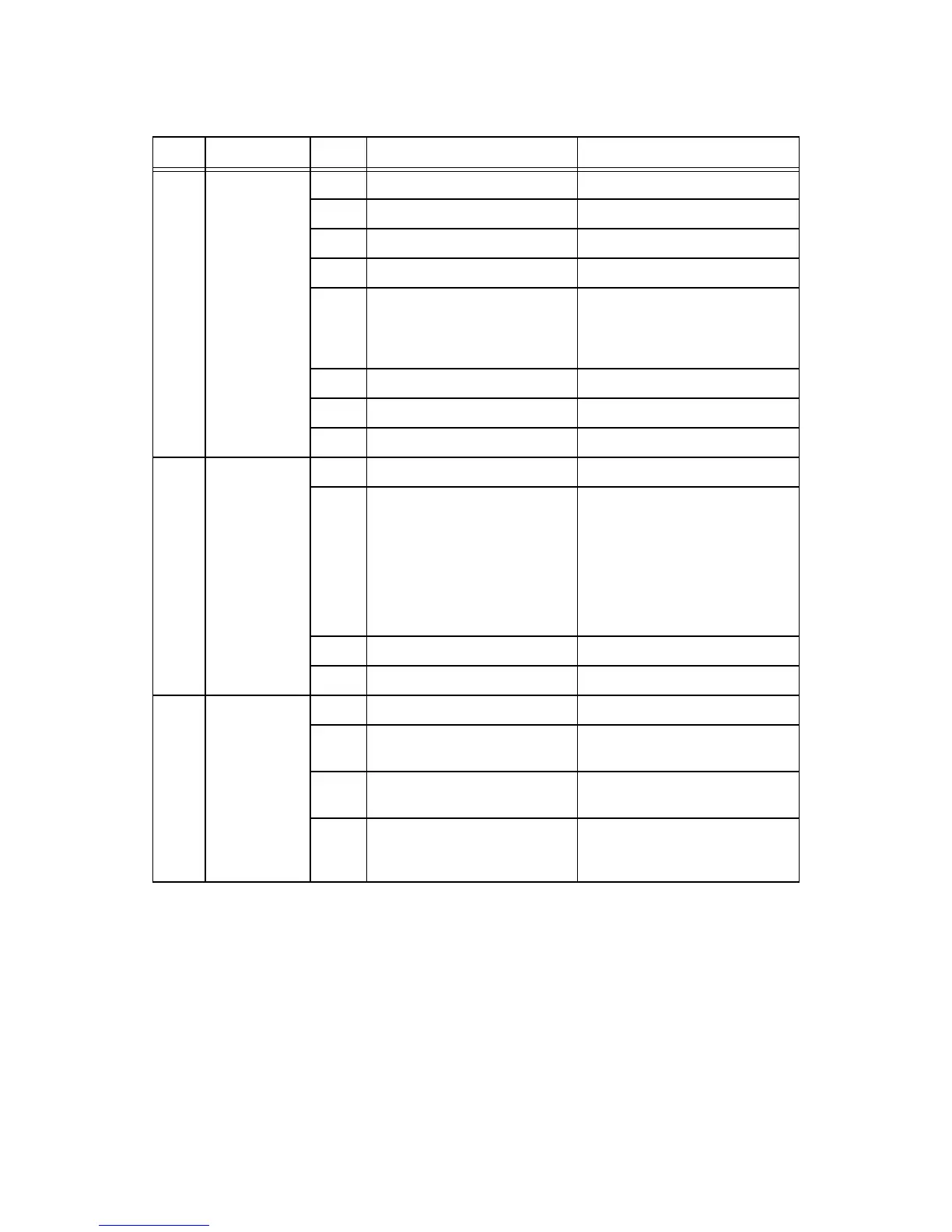

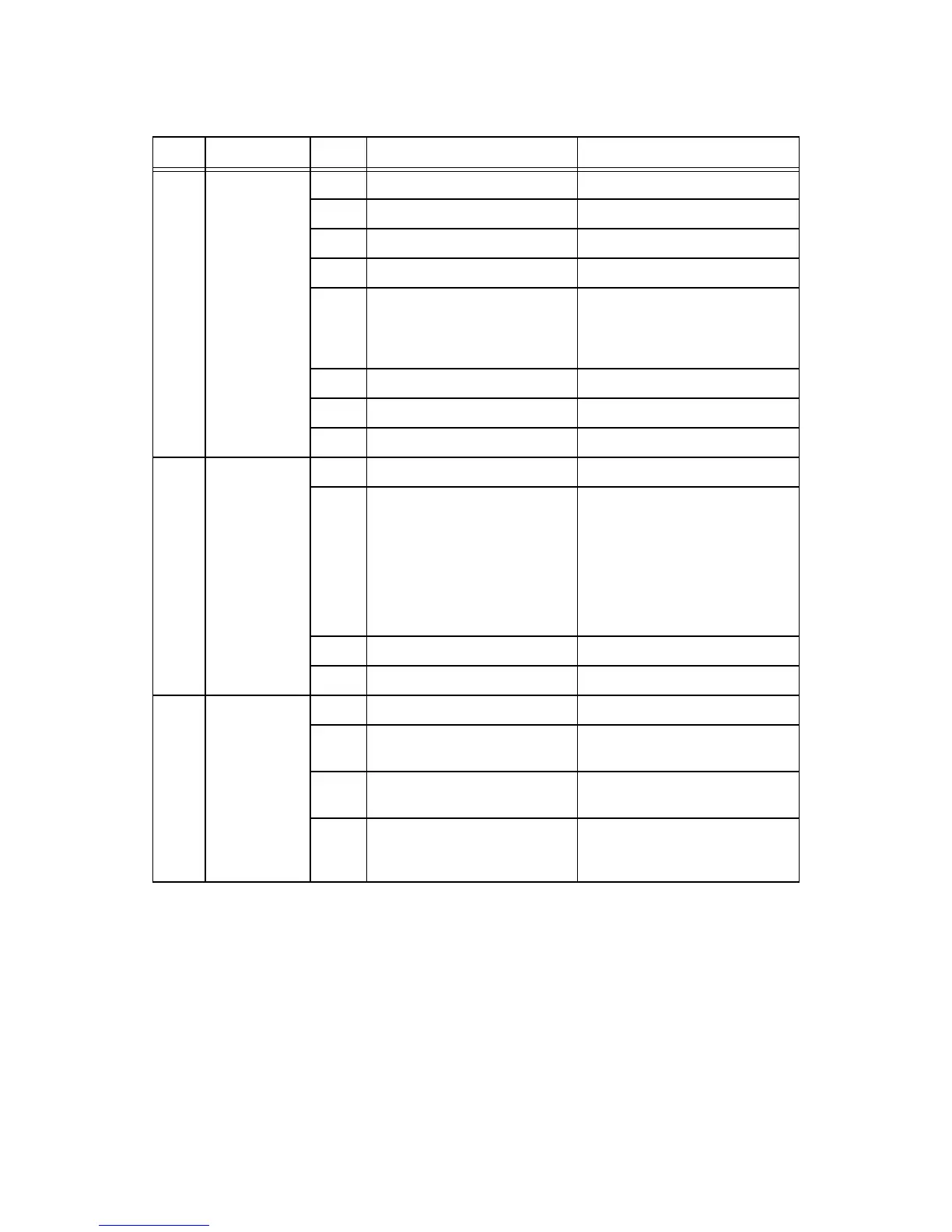

J26

Even

RESET Clock CLK_1KHZ 1 KHz

15 CLK_32KHZ 32 KHz

14:13 DVSB_OK, SB_RSTN Stand-by Reset control

12:5 FRSTN, EJRSTN, ATX_OK,

CBUS_FPGA_OK, D5V_OK,

D3V3_OK, POWER_OK,

CORE_OK

Reset control

4:2 FPGA_RSTN, RSTN, RST RESET outputs

1 PAR_ENAB Parallel download

0 CPRESN Core card present

J26

Odd

CBUS FPGA Clock PCI_CLK 33.33 MHz (default)

15:2 CPU_INTN5, CPU_INTN4,

CPU_INTN3, CPU_INTN2,

CPU_INTN1, CPU_INTN0,

CPU_NMIN,

SOUTHBRIDGE_INT,

SOUTHBRIDGE_NMI,

SOUTHBRIDGE_SMIN,

UINT, CINTHIN, CINTLON

Interrupts

2:1 Not used

0 ISA_SERIRQ Super I/O Interrupts

J27

Even

JTAG + PCI Clock CLK_40MHZ 40 MHz

15:10 EJTRSTN, EJTDO, EJTDI,

EJTMS, EJTCK, EJDINT

JTAG signals

9:6 PCI_INTAN, PCI_INTBN,

PCI_INTCN, PCI_INTDN

PCI Interrupts

5:0 PCI_FRAMEN, PCI_IRDYN,

PCI_TRDY, PCI_DEVSELN,

PCI_STOPN, PCI_LOCKN

PCI signals

Table 5.6 Logic Analyser Connectors (Continued)

Ref Function Bits Signals Description

Loading...

Loading...