“Confidential, Do Not Duplicate without written authorization from NEC.”

8-33

CIRCUIT DESCRIPTION

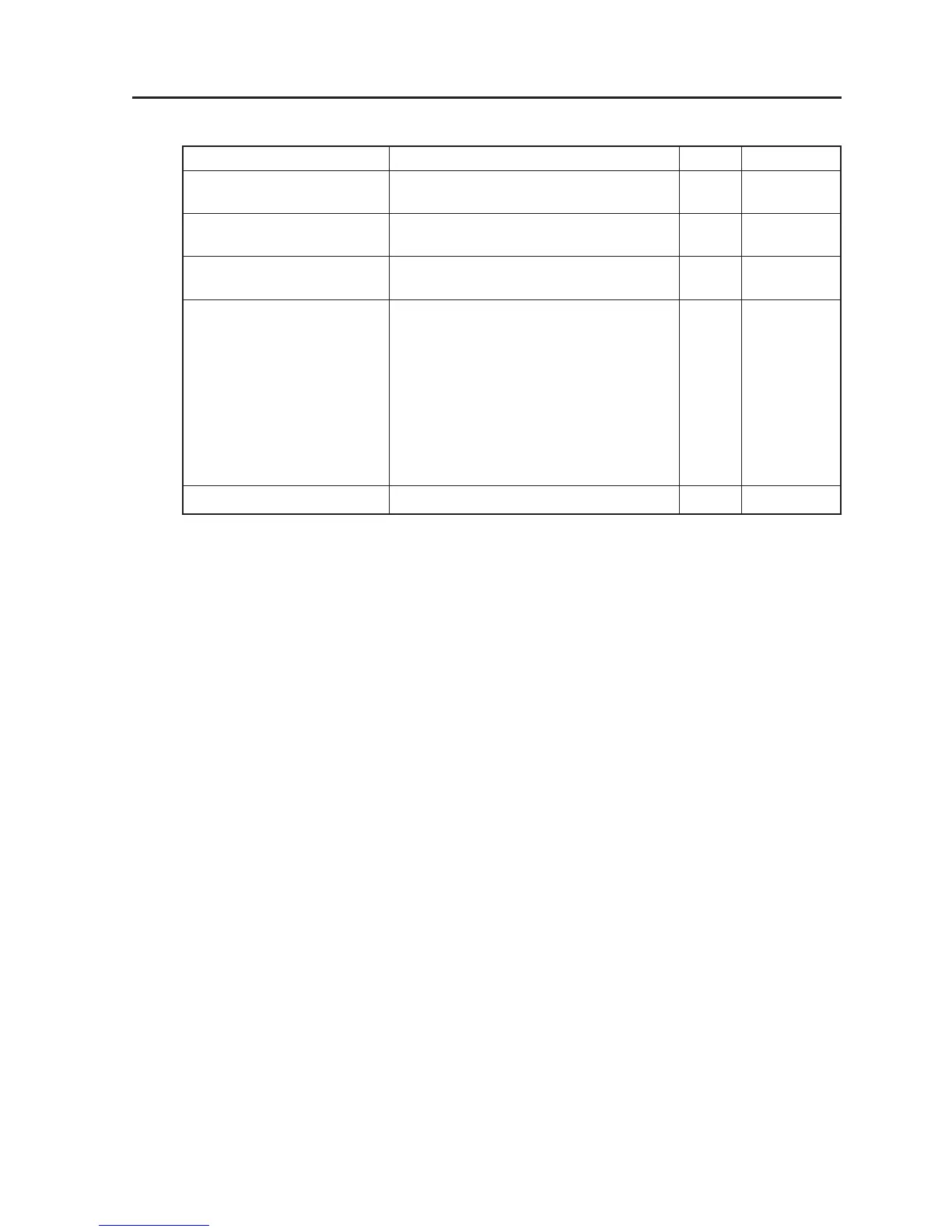

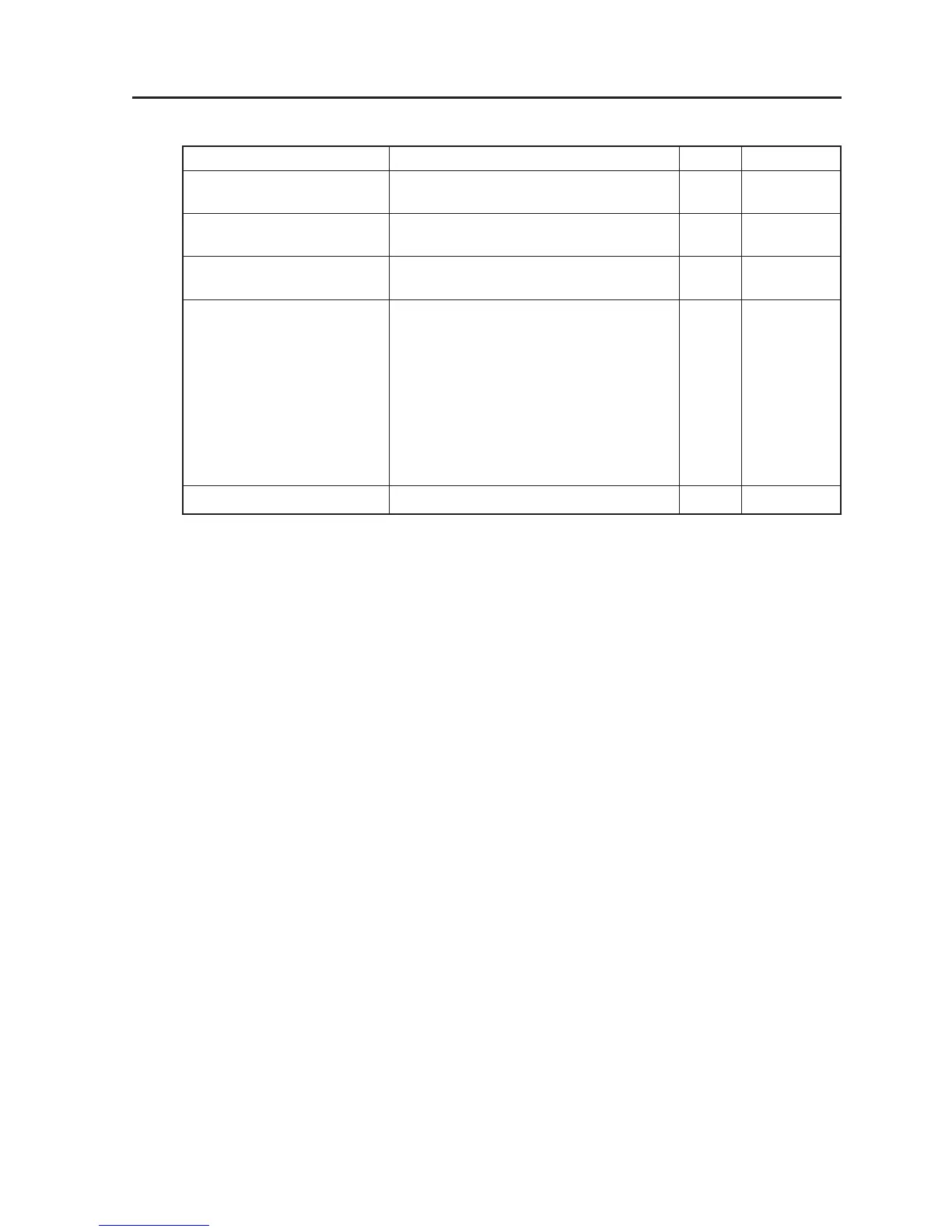

Signal Name Description I/O Type

SAT_ CCLK Data Clock ? used to time C_DATA input I 2.5V LVCMOS

during configuration.

SAT_DIN Configuration Data? serial data input used O 2.5V LVCMOS

to configure the device.

SAT_DONE Configuration Done? indicates completion I 2.5V LVCMOS

of device configuration.

SAT_INIT_B Before MODE pins are sampled, SAT_INIT I/O 2.5V LVCMOS

is an input that can be held Low to delay

configuration.

After MODE pins are sampled, SAT_INIT

is an open-drain active Low output

indicating whether a CRC error occurred

during configuration :

0 = CRC error

1 = No CRC error

SAT_PROG_B FPGA Full-chip reset (Active LOW) I 2.5V LVCMOS

1-6. Satellite FPGA Programming Interface

Loading...

Loading...