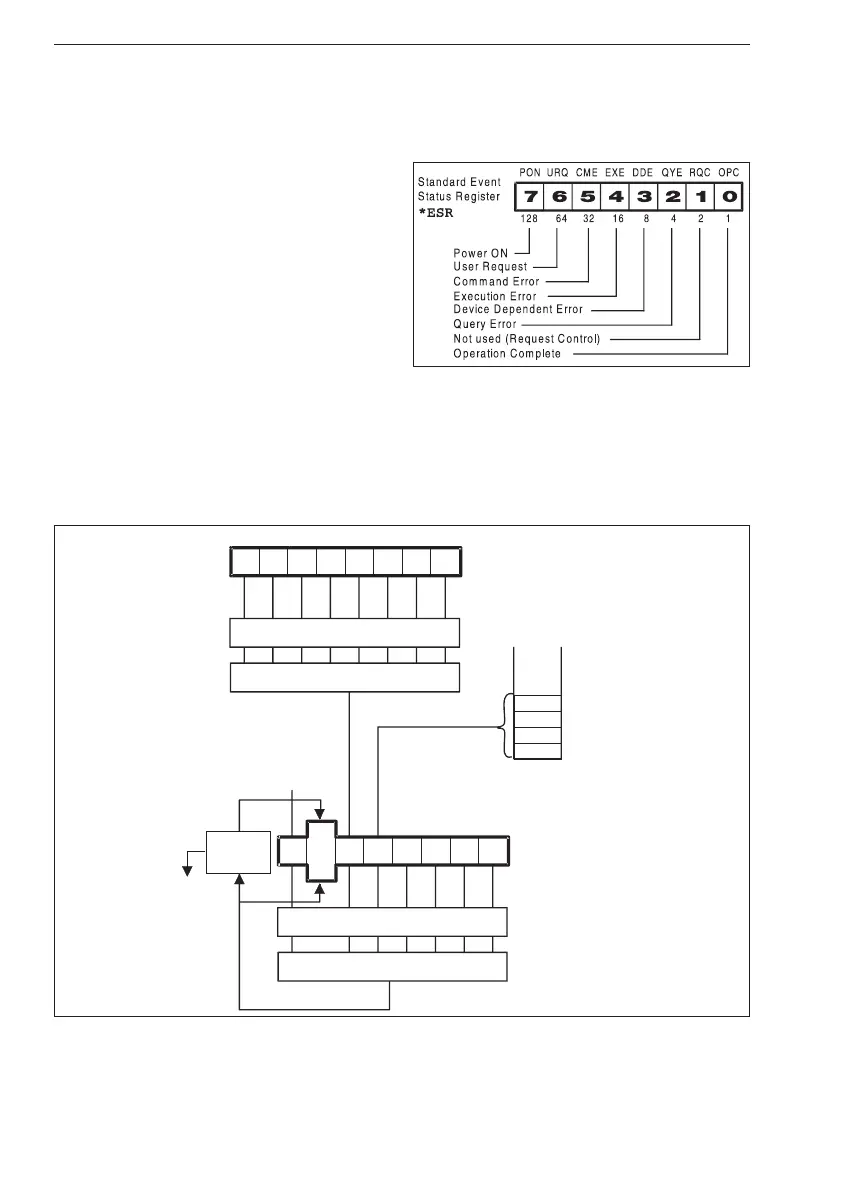

Standard Status Registers

These registers are called the standard

status data structure because they are

mandatory in all instruments that fulfill

the IEEE 488.2 standard.

n

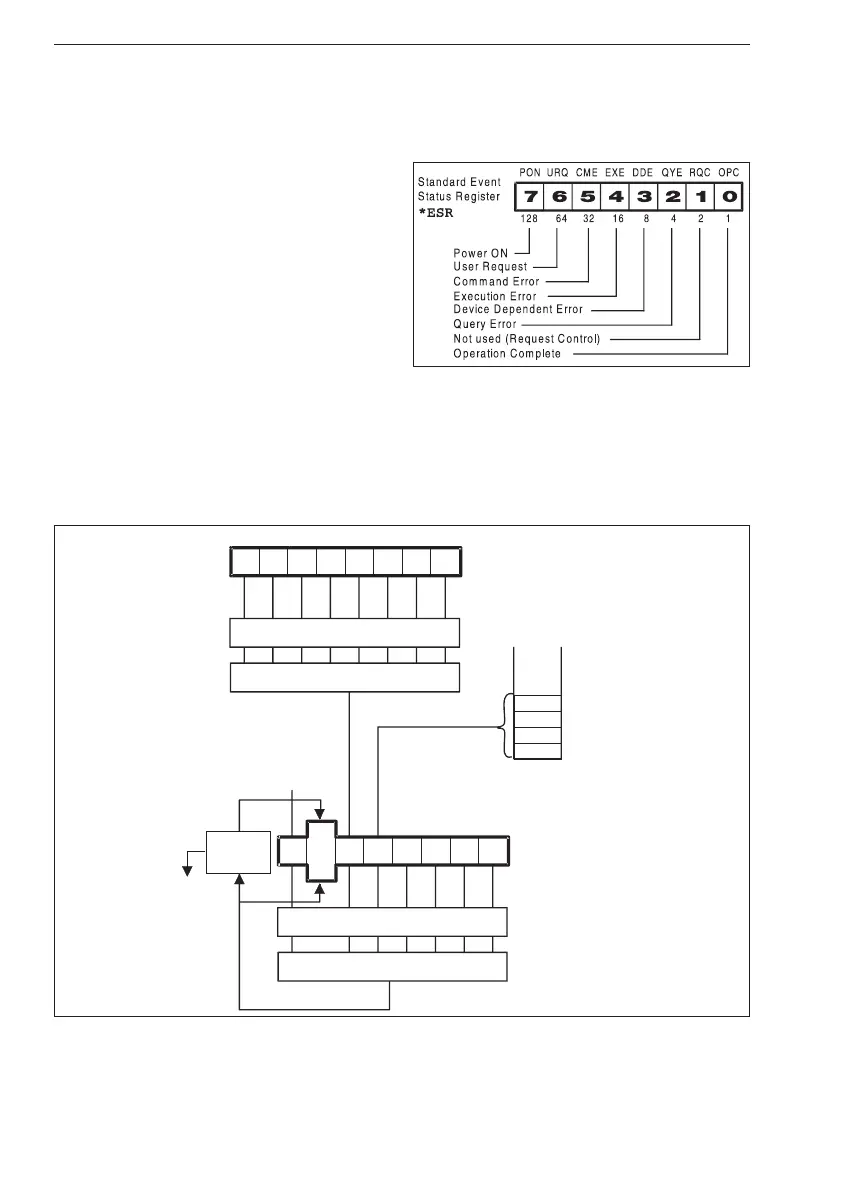

Standard Event Status Register

Bit 7 (weight 128) — Power-on (PON)

Shows that the counter’s power supply has

been turned off and on (since the last time

the controller read or cleared this register).

Bit 6 (weight 64)—User Request (URQ)

Shows that the user has pressed a key on

the front panel. The URQ bit will be set

regardless of the remote local state of the

counter. The purpose of this signal is, for

example, to call for the attention of the

controller by generating a service request.

6-16 Status Subsystem

Using the Subsystems

Output Queue not empty

<...read by *STB?

Service Request Enable

Logical OR

Status Byte

Register

SRQ

signal

16

RQS

MSS

ESB MAV

Service

Request

Generation

Standard Event Status Enable

Logical OR

16754320

Output

Queue

132 0

7

*ESE <NRf>

*ESE?

* SRE <NRf >

*SRE?

Standard Event

Status Register

*ESR?

PON

URQ

CME EXE DDE

QYE

RQC

OPC

Figure 6-4 Standard status data structures, overview.

Figure 6-5 Bits in the standard event

status register

Loading...

Loading...