R8C/20 Group, R8C/21 Group 13. Watchdog Timer

Rev.2.00 Aug 27, 2008 Page 115 of 458

REJ09B0250-0200

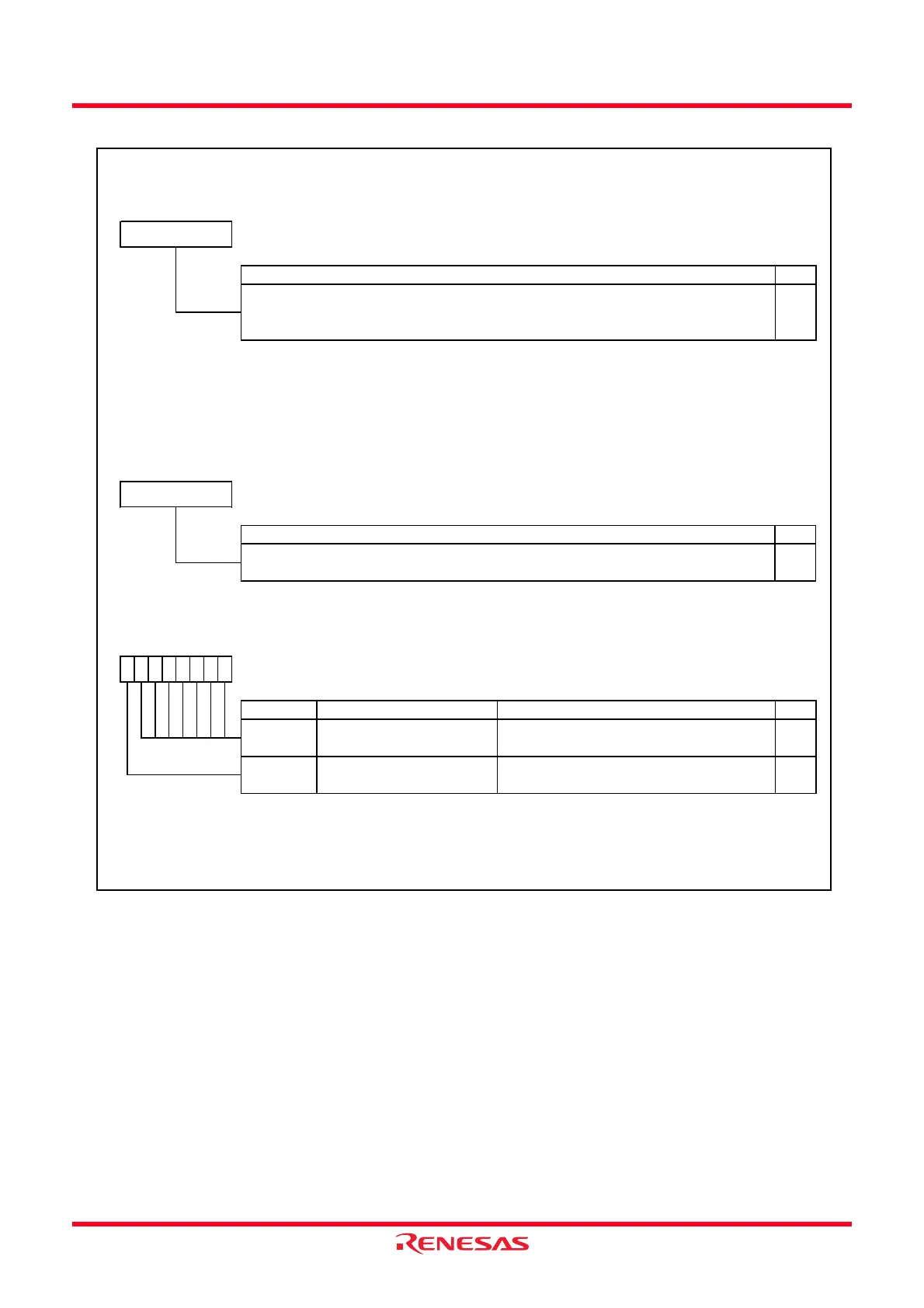

Figure 13.3 Registers WDTR, WDTS, and CSPR

Watchdog Timer Reset Register

Symbol Address After Reset

WDTR

000Dh Indeterminate

RW

NOTES:

1.

2.

Function

When w riting 00h before w riting FFh, the watchdog timer is reset.

(1)

The default value of the w atchdog timer is set to 7FFFh w hen count source protection

mode is disabled and 0FFFh w hen count source protection mode is enabled.

(2)

b7 b0

Do not generate an interrupt betw een 00h and the FFh w ritings.

When the CSPRO bit in the CSPR register is set to 1 (count source protection mode enabled),

0FFFh is set to the w atchdog timer.

WO

Watchdog Timer Start Register

Symbol Address After Reset

WDTS

000Eh Indeterminate

RW

WO

Function

The w atchdog timer starts counting after a w rite instruction to this register.

b0b7

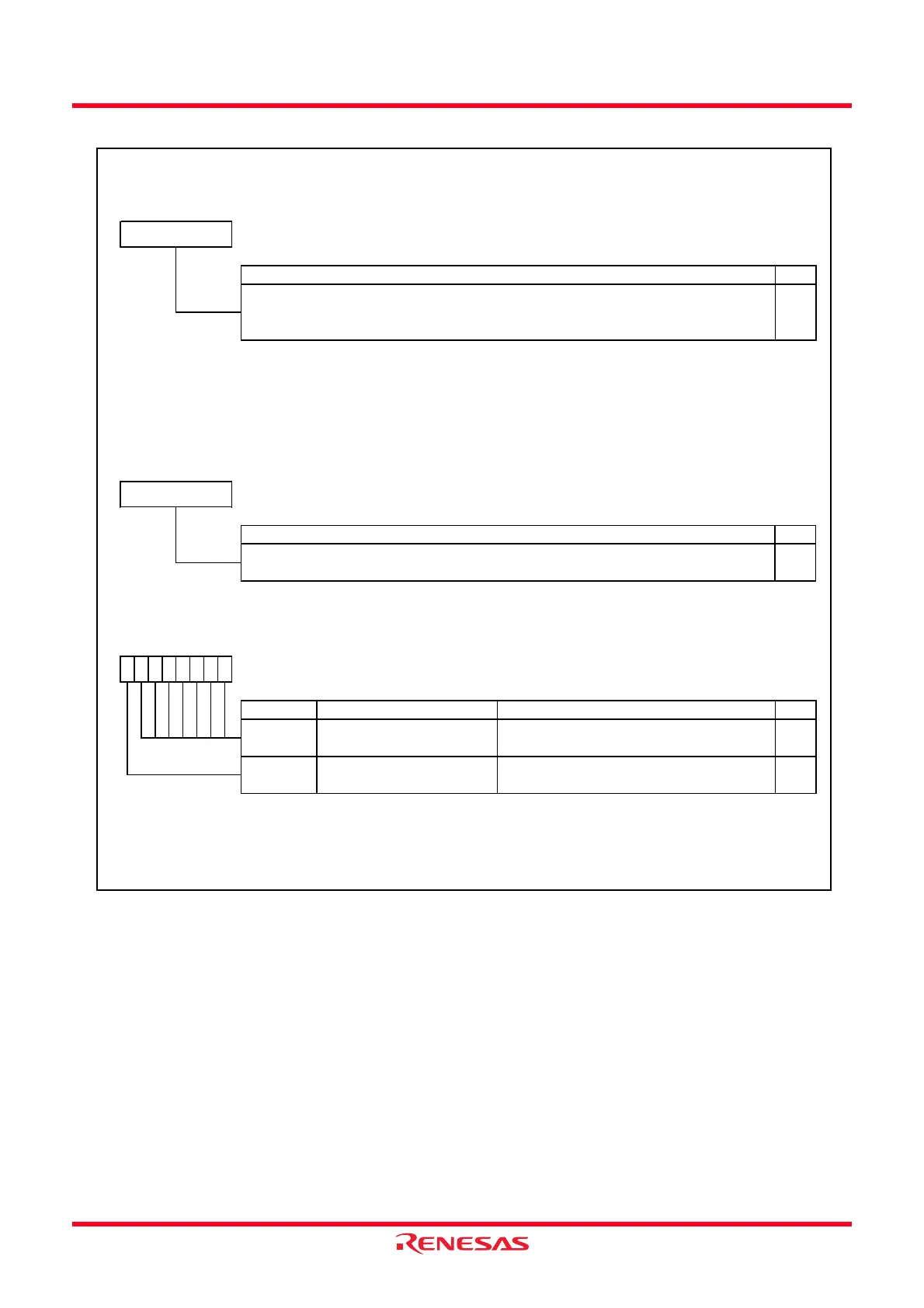

Count Source Protection Mode Register

Symbol Address After Reset

(1)

CSPR

001Ch 00h

Bit Symbol Bit Name Function RW

NOTES:

1.

2.

—

(b6-b0)

RW

00

Write 0 before w riting 1 to set the CSPRO bit to 1.

0 cannot be set by a program.

When w riting 0 to the CSPROINI bit in the OFS register, the value after reset is set to 10000000b.

0

Reserved bits Set to 0

b3 b2 b1 b0b7 b6 b5 b4

RW

0000

CSPRO

Count source protection mode

select bit

(2)

0 : Count source protection mode disabled

1 : Count source protection mode enabled

Loading...

Loading...