R8C/20 Group, R8C/21 Group 14. Timers

Rev.2.00 Aug 27, 2008 Page 171 of 458

REJ09B0250-0200

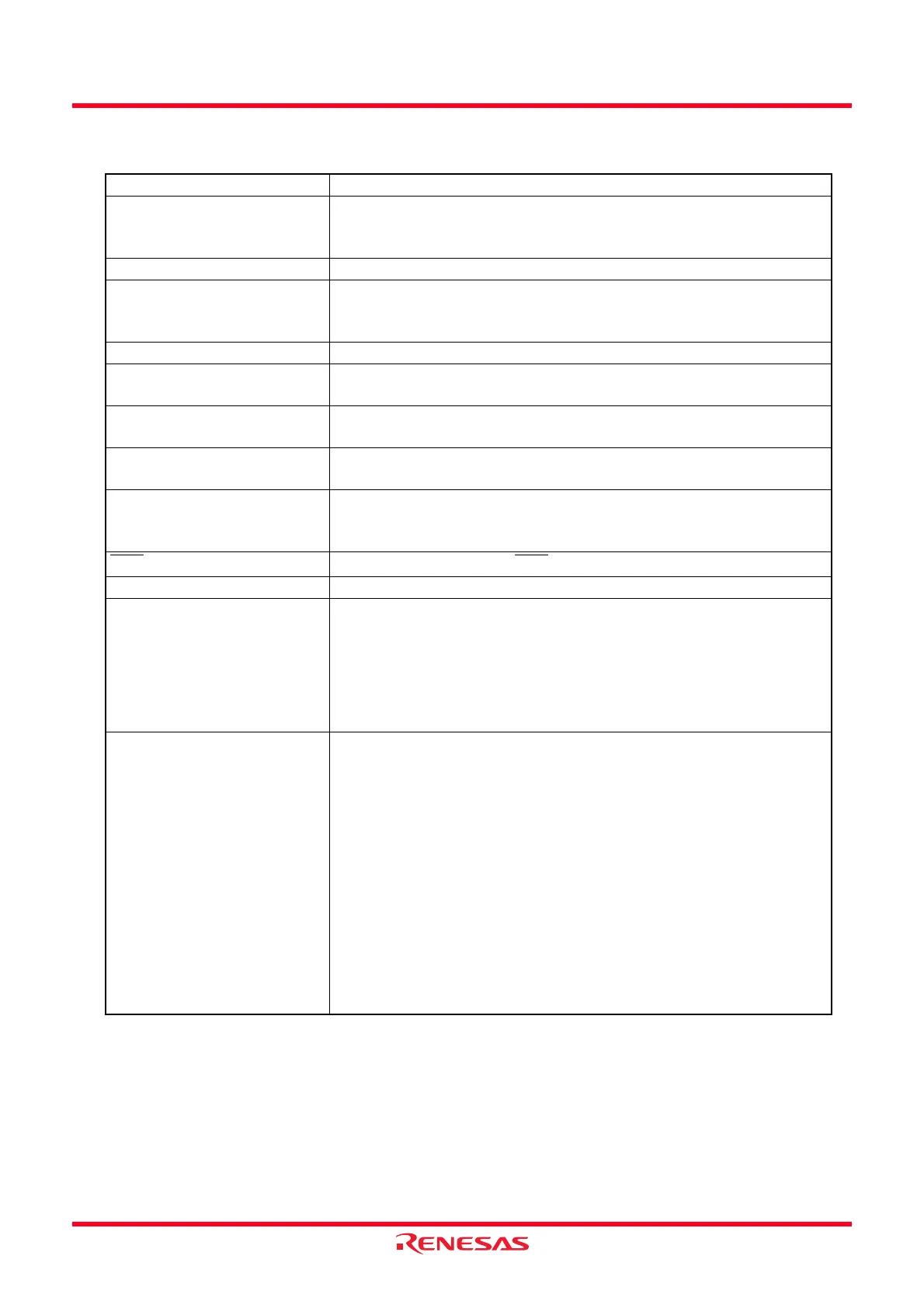

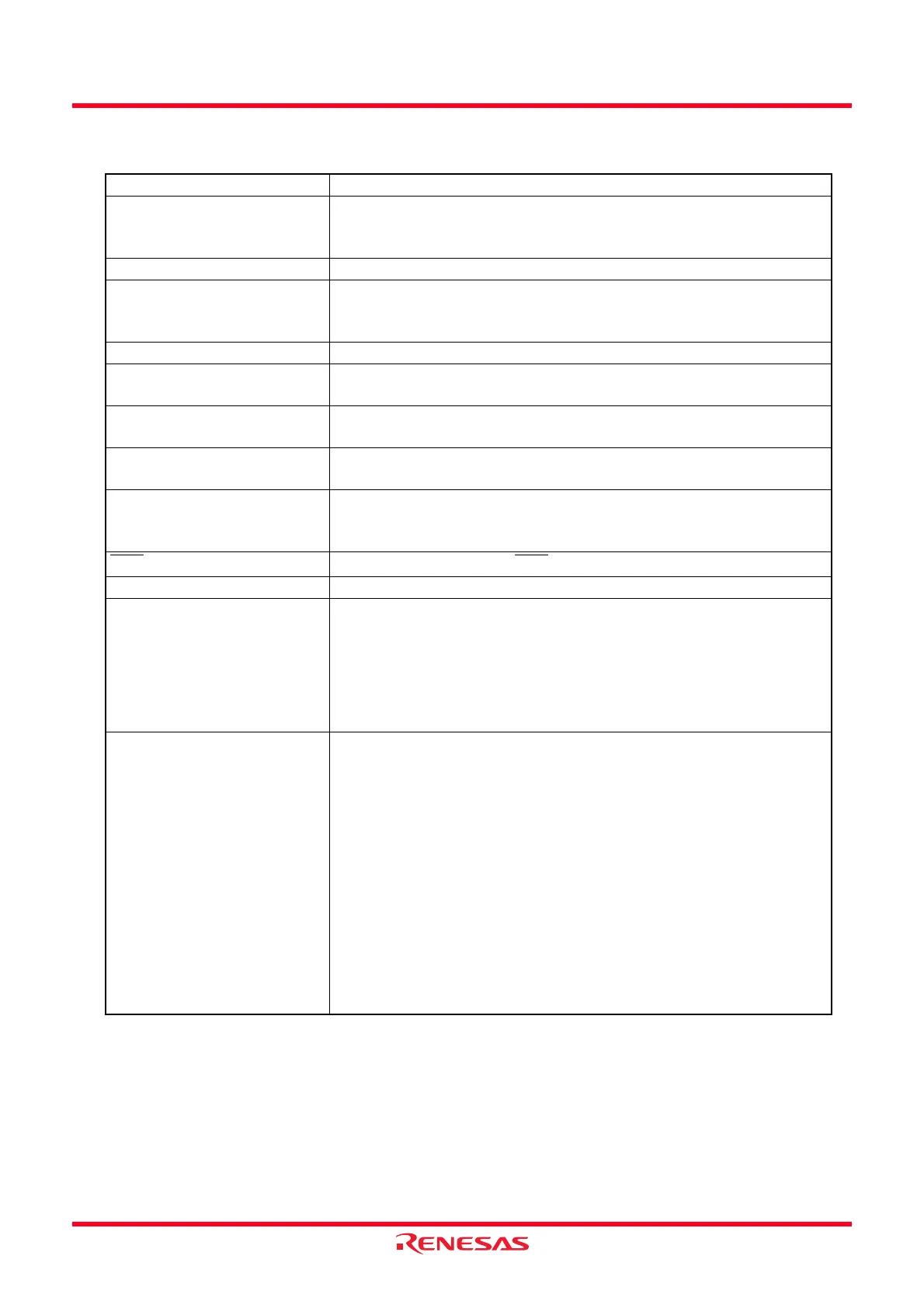

i = 0 or 1, j = either A, B, C or D

Table 14.23 Input Capture Function Specifications

Item Specification

Count Sources f1, f2, f4, f8, f32, fOCO40M

External signal input to the TRDCLK pin (valid edge selected by a

program)

Count Operations Increment

Count Period When the CCLR2 to CCLR0 bits in the TRDCRi register are set to 000b

(free-running operation).

1/fk × 65536 fk: Frequency of count source

Count Start Condition Write 1 (count starts) to the TSTARTi bit in the TRDSTR register.

Count Stop Condition Write 0 (count stops) to the TSTARTi bit in the TRDSTR register when

the CSELi bit in the TRDSTR register is set to 1.

Interrupt Request Generation

Timing

• Input capture (valid edge of TRDIOji input or fOCO128 signal edge)

• TRDi register overflows

TRDIOA0 Pin Function Programmable I/O port, input-capture input, or TRDCLK (external clock)

input

TRDIOB0, TRDIOC0,

TRDIOD0, TRDIOA1 to

TRDIOD1 Pin Functions

Programmable I/O port, or input-capture input

(Select every pin)

INT0

Pin Function Programmable I/O port or INT0 interrupt input

Read from Timer The count value can be read by reading the TRDi register.

Write to Timer • When the SYNC bit in the TRDMR register is set to 0 (channels 0 and

1 operate independently).

• Data can be written to the TRDi register.

• When the SYNC bit in the TRDMR register is set to 1 (channels 0 and

1 operate synchronously.)

• Data can be written to both the TRD0 and TRD1 registers by writing to

the TRDi register.

Selection Functions • Input-capture input pin selected

Either 1 pin or multiple pins of the TRDIOAi, TRDIOBi, TRDIOCi or

TRDIODi pin.

• Input-capture input valid edge selected

The rising edge, falling edge or both the rising and falling edges

• The timing when the TRDi register is set to 0000h

At overflow or input capture

• Buffer operation (refer to 14.3.2 Buffer Operation)

• Synchronous operation (refer to 14.3.3 Synchronous Operation)

• Digital filter

The TRDIOji input is sampled, and when the sampled input level match

3 times, its level is assumed as a determination.

• Input-capture trigger selected

fOCO128 can be selected for input-capture trigger input of the

TRDGRA0 register.

Loading...

Loading...