R8C/20 Group, R8C/21 Group 14. Timers

Rev.2.00 Aug 27, 2008 Page 218 of 458

REJ09B0250-0200

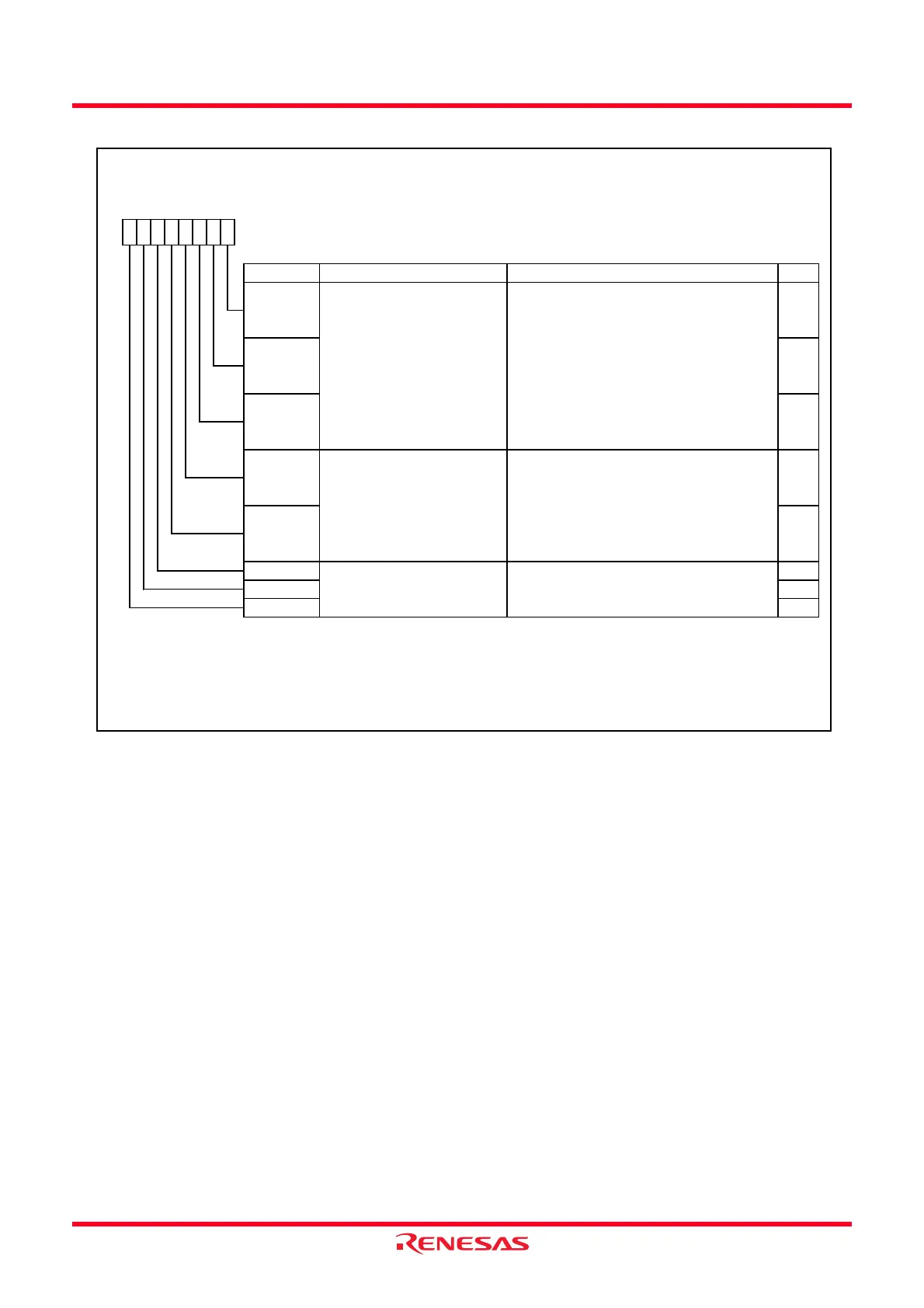

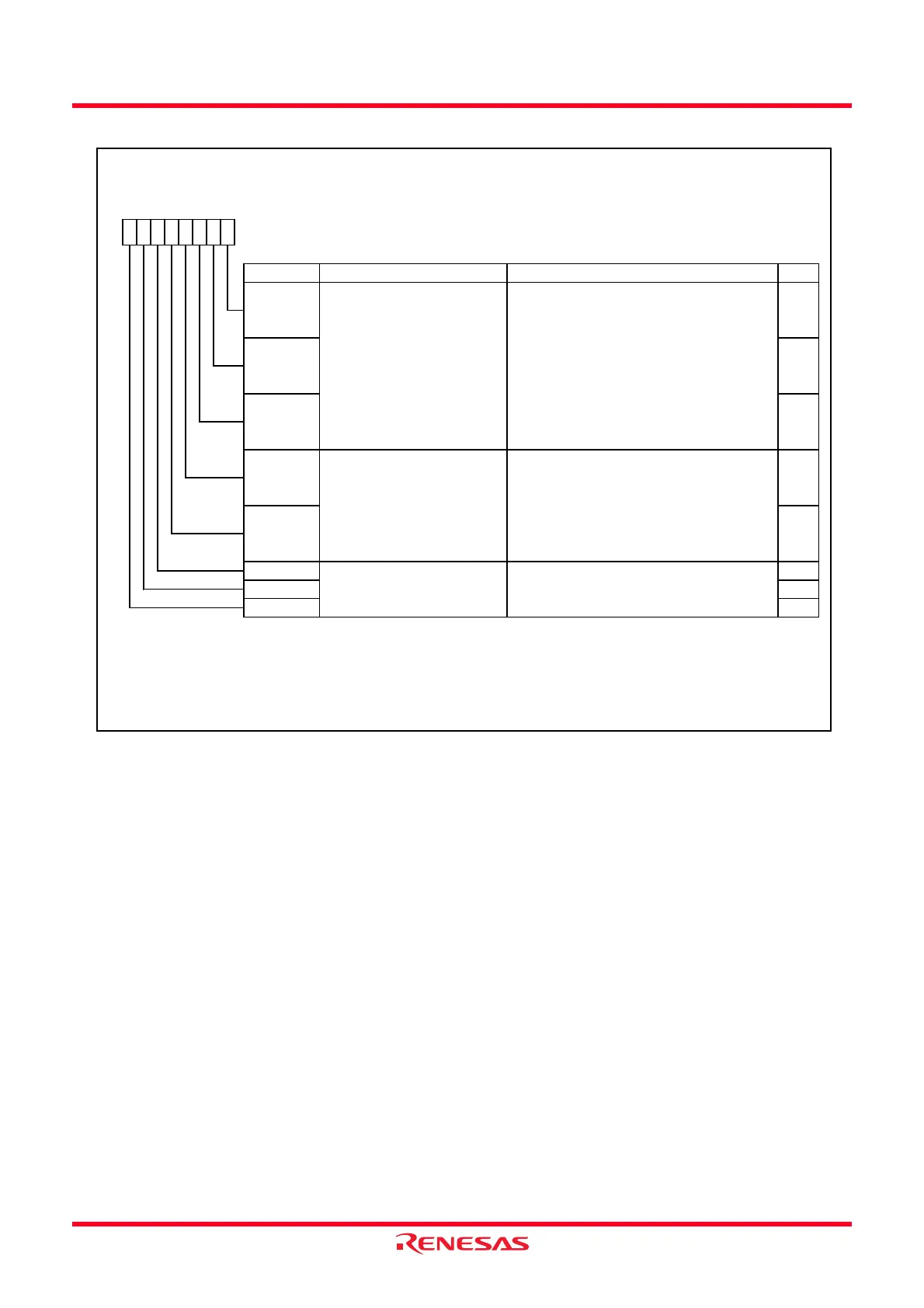

Figure 14.80 TRDCR0 Register in Reset Synchronous PWM Mode

Timer RD Control Register 0

(3)

Symbol Address After Reset

TRDCR0

0140h 00h

Bit Symbol Bit Name Function RW

NOTES:

1.

2.

3.

RW

TCK1 RW

TCK0

RW

RW

RW

CCLR2

CCLR1 RW

Count source selection bit

b2 b1b0

0 0 0 : f1

0 0 1 : f2

0 1 0 : f4

0 1 1 : f8

1 0 0 : f32

1 0 1 : TRDCLK input

(1)

1 1 0 : fOCO40M

1 1 1 : Do not set

External clock edge selection

bit

(2)

b4 b3

0 0 : Count at the rising edge

0 1 : Count at the falling edge

1 0 : Count at both edges

1 1 : Do not set

b7 b6 b5 b4

001

b3 b2

CKEG0

b1 b0

TCK2

The TRDCR1 register is not used in reset synchronous PWM mode.

This bit is enabled w hen the TCK2 to TCK0 bits are set to “101b” (TRDCLK input) and the STCLK bit in the TRDFCR

register is set to 1 (external clock input enabled).

RW

CKEG1

CCLR0 RWSet to 001b (TRD0 register clear at the

compare match w ith TRDGRA0 register) in

reset synchronous PWM mode.

TRD0 counter clear selection bit

This bit is enabled w hen the STCLK bit in the TRDFCR register is set to 1 (external clock input enabled).

Loading...

Loading...