R8C/20 Group, R8C/21 Group 15. Serial Interface

Rev.2.00 Aug 27, 2008 Page 278 of 458

REJ09B0250-0200

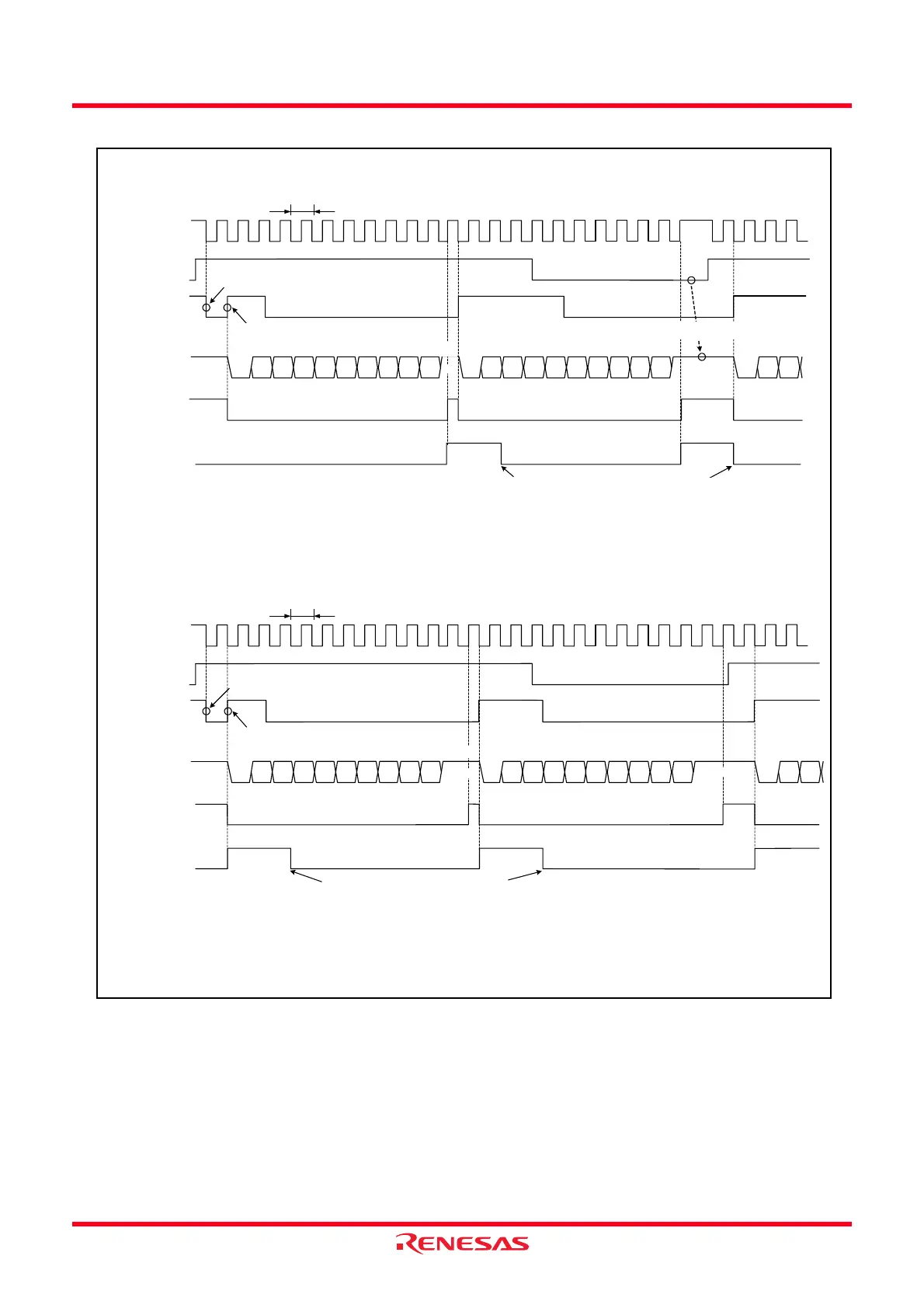

Figure 15.10 Transmit Timing in UART Mode

D0

TC

D1 D2 D3 D4 D5 D6 D7 P

SP

ST D0 D1 D2 D3 D4 D5 D6 D7 P SPST D0 D1ST

D0

TC

D1 D2 D3 D4 D5 D6 D7 D8

SP SP

ST D0 D1 D2 D3 D4 D5 D6 D7 D8 SP SPST D0 D1ST

Transfer clock

TE bit in UiC1

register

TXDi

Set to 0 when interrupt request is acknowledged, or set by a program

• Transmit timing when transfer data is 8 bits long (parity enabled, 1 stop bit)

Write data to UiTB register

TC=16 (n + 1) / fj or 16 (n + 1) / fEXT

fj: Frequency of UiBRG count source (f1, f8, f32)

fEXT: Frequency of UiBRG count source (external clock)

n: Setting value to UiBRG register

i = 0 or 1

The above timing diagram applies under the following conditions:

• PRYE bit in UiMR register = 1 (parity enabled)

• STPS bit in UiMR register = 0 (1 stop bit)

• UiIRS bit in UiC1 register = 1 (an interrupt request is generated when transmit completes)

Start

bit

Parity

bit

Stop pulsing

because the TE bit is set to 0

TXDi

Write data to UiTB register

Transfer from UiTB register to UARTi transmit register

TI bit in UiC1

register

1

0

1

0

1

0

1

0

TXEPT bit in

UiC0 register

IR bit SiTIC

register

Stop

bit

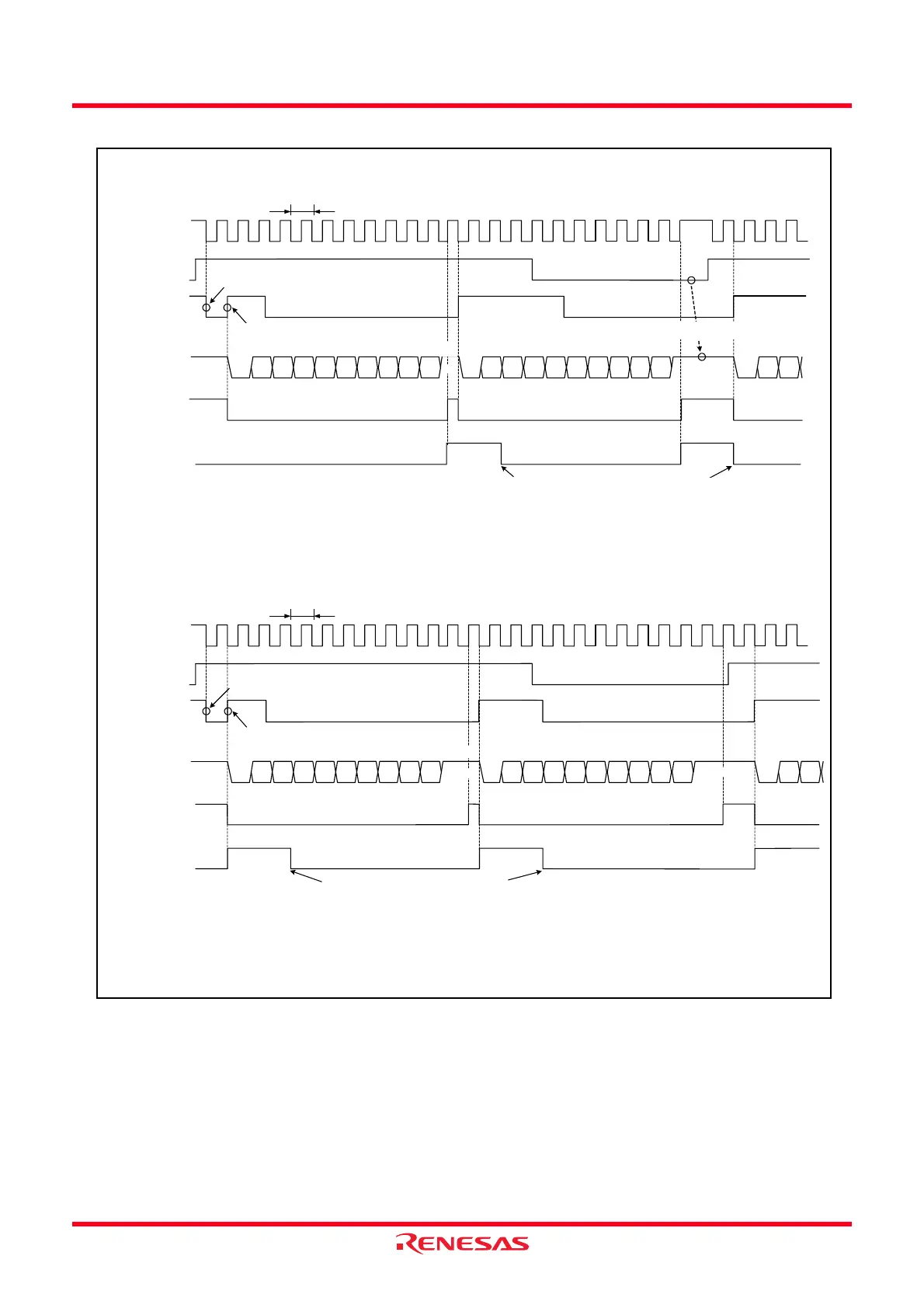

• Transmit timing when transfer data is 9 bits long (parity disabled, 2 stop bits)

1

0

Stop

bit

Stop

bit

Start

bit

Transfer clock

TE bit in UiC1

register

TI bit in UiC1

register

TXEPT bit in

UiC0 register

IR bit in SiTIC

register

1

0

1

0

1

0

Transfer from UiTB register to UARTi transmit register

TC=16 (n + 1) / fj or 16 (n + 1) / fEXT

fj: Frequency of UiBRG count source (f1, f8, f32)

fEXT: Frequency of UiBRG count source (external clock)

n: Setting value to UiBRG register

i = 0 or 1

Set to 0 when interrupt request is acknowledged, or set by a program

The above timing diagram applies under the following conditions:

• PRYE bit in UiMR register = 0 (parity disabled)

• STPS bit in UiMR register = 1 (2 stop bits)

• UiIRS bit in UiC1 register = 0 (an interrupt request is generated when transmit buffer is empty)

Loading...

Loading...