R8C/20 Group, R8C/21 Group 15. Serial Interface

Rev.2.00 Aug 27, 2008 Page 279 of 458

REJ09B0250-0200

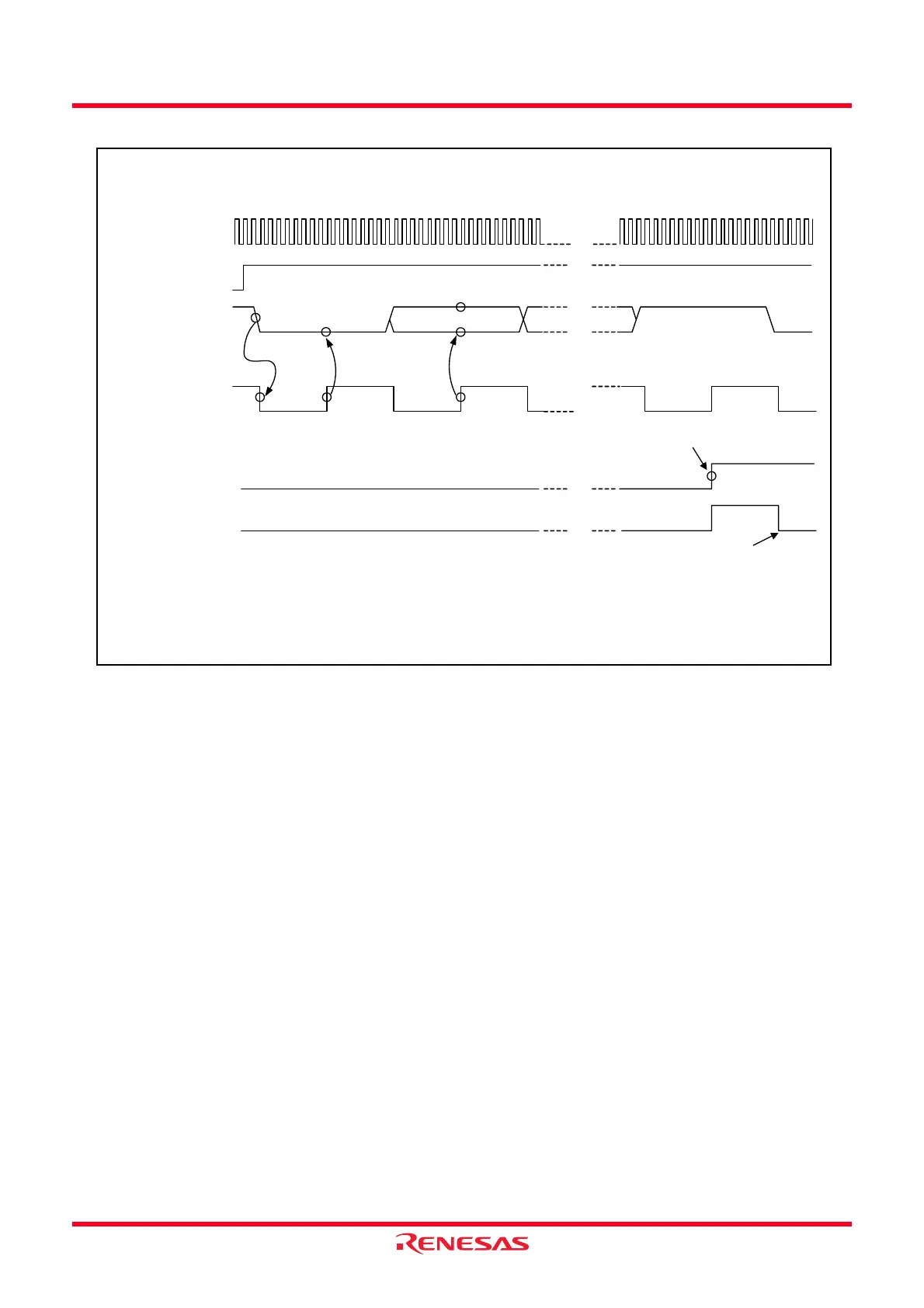

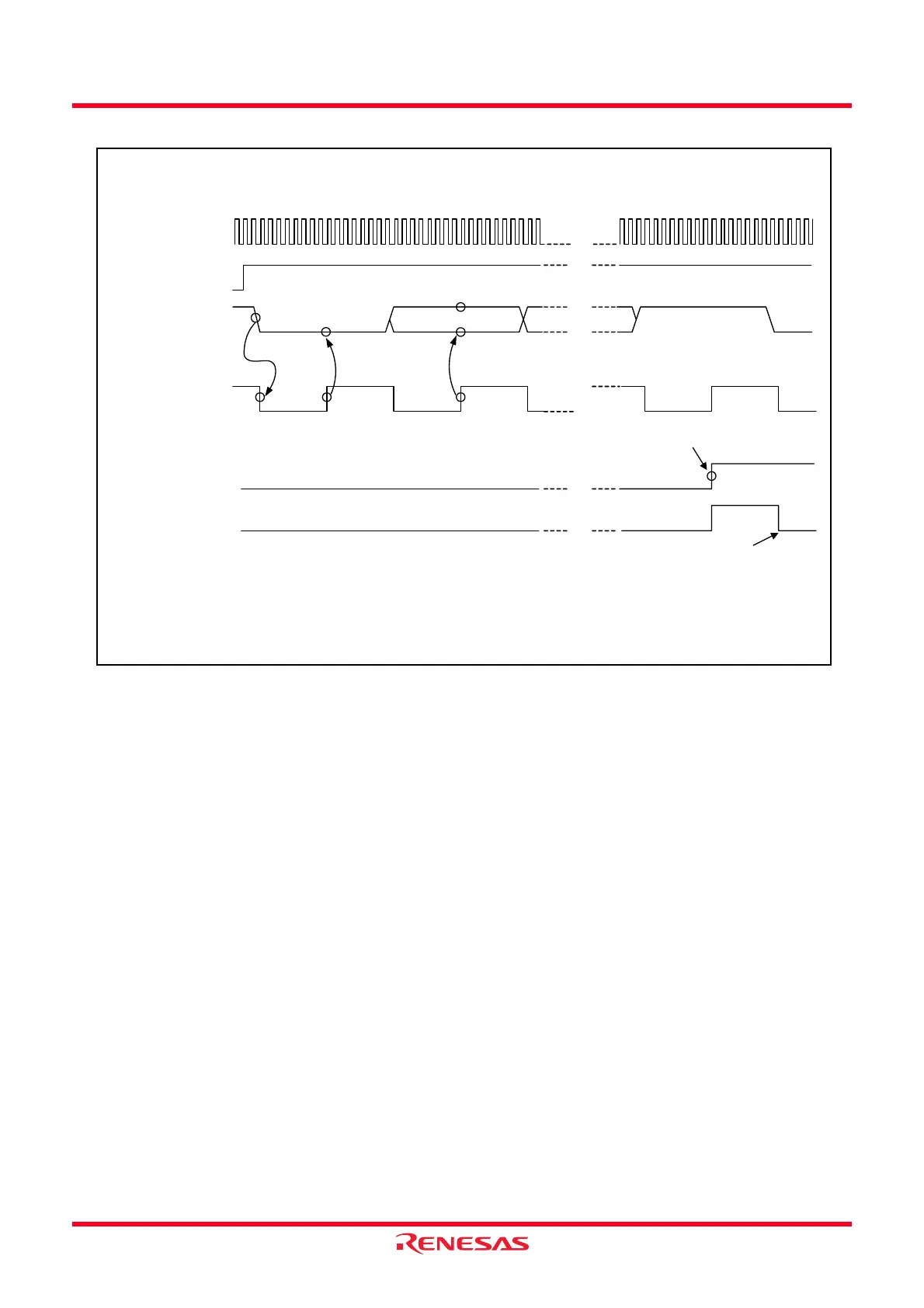

Figure 15.11 Receive Timing Example in UART Mode

UiBRG output

Set to 0 when interrupt request is accepted, or set by a program

• Example of Receive Timing when Transfer Data is 8 Bits Long (parity disabled, one stop bit)

The above timing diagram applies to the case where the register bits are set as follows:

• UiMR register PRYE bit = 0 (parity disabled)

• UiMR register STPS bit = 0 (1 stop bit)

i = 0 or 1

UiC1 register

RE bit

Start bit

Stop bit

D0 D1 D7

RXDi

Transfer clock

Determined “L”

Receive data taken in

Reception triggered when transfer clock

is generated by falling edge of start bit

Transferred from UARTi receive

register to UiRB register

UiC1 register

RI bit

SiRIC register

RI bit

1

0

1

0

1

0

Loading...

Loading...