R8C/20 Group, R8C/21 Group 16. Clock Synchronous Serial Interface

Rev.2.00 Aug 27, 2008 Page 288 of 458

REJ09B0250-0200

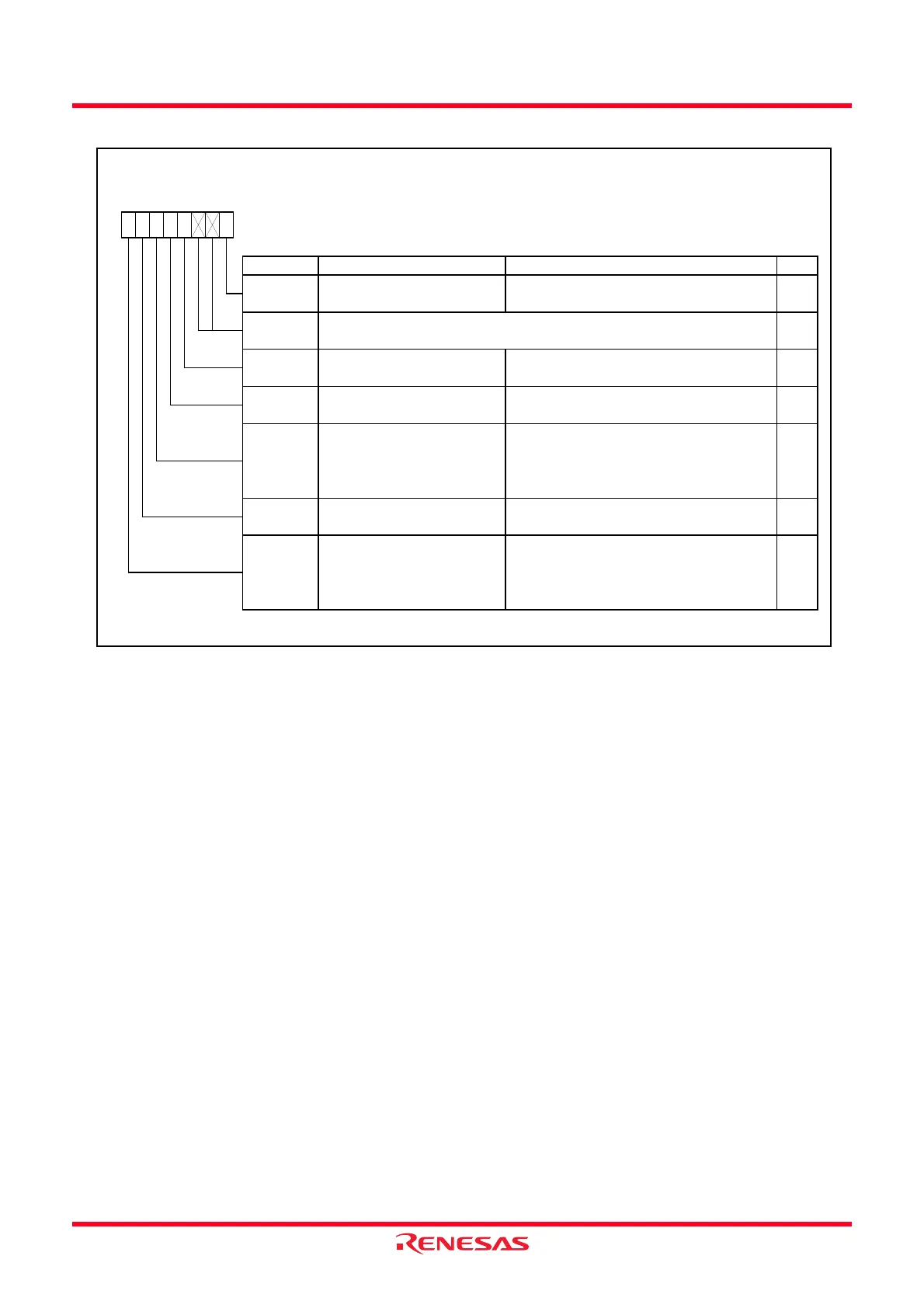

Figure 16.5 SSER Register

SS Enable Register

Symbol Address After Reset

SSER

00BBh 00h

Bit Symbol Bit Name Function RW

b0b3 b2 b1b7 b6 b5 b4

RW

RW

RW

—

Conflict error interrupt enable bit 0 : Disables conflict error interrupt request

1 : Enables conflict error interrupt request

—

(b2-b1)

Nothing is assigned. If necessary, set to 0.

When read, the content is 0.

CEIE

0 : Disables transmit data empty interrupt

request

1 : Enables transmit data empty interrupt

request

0 : Disables transmit end interrupt request

1 : Enables transmit end interrupt request

RW

RE

TE

TEIE

Transmit end interrupt enable bit

RW

RIE RW

Receive enable bit 0 : Disables receive

1 : Enables receive

Transmit enable bit 0 : Disables transmit

1 : Enables transmit

0 : Disables receive data full and overrun

error interrupt request

1 : Enables receive data full and overrun

error interrupt request

Receive interrupt enable bit

TIE

Transmit interrupt enable bit

Loading...

Loading...