R8C/20 Group, R8C/21 Group 19. Flash Memory

Rev.2.00 Aug 27, 2008 Page 396 of 458

REJ09B0250-0200

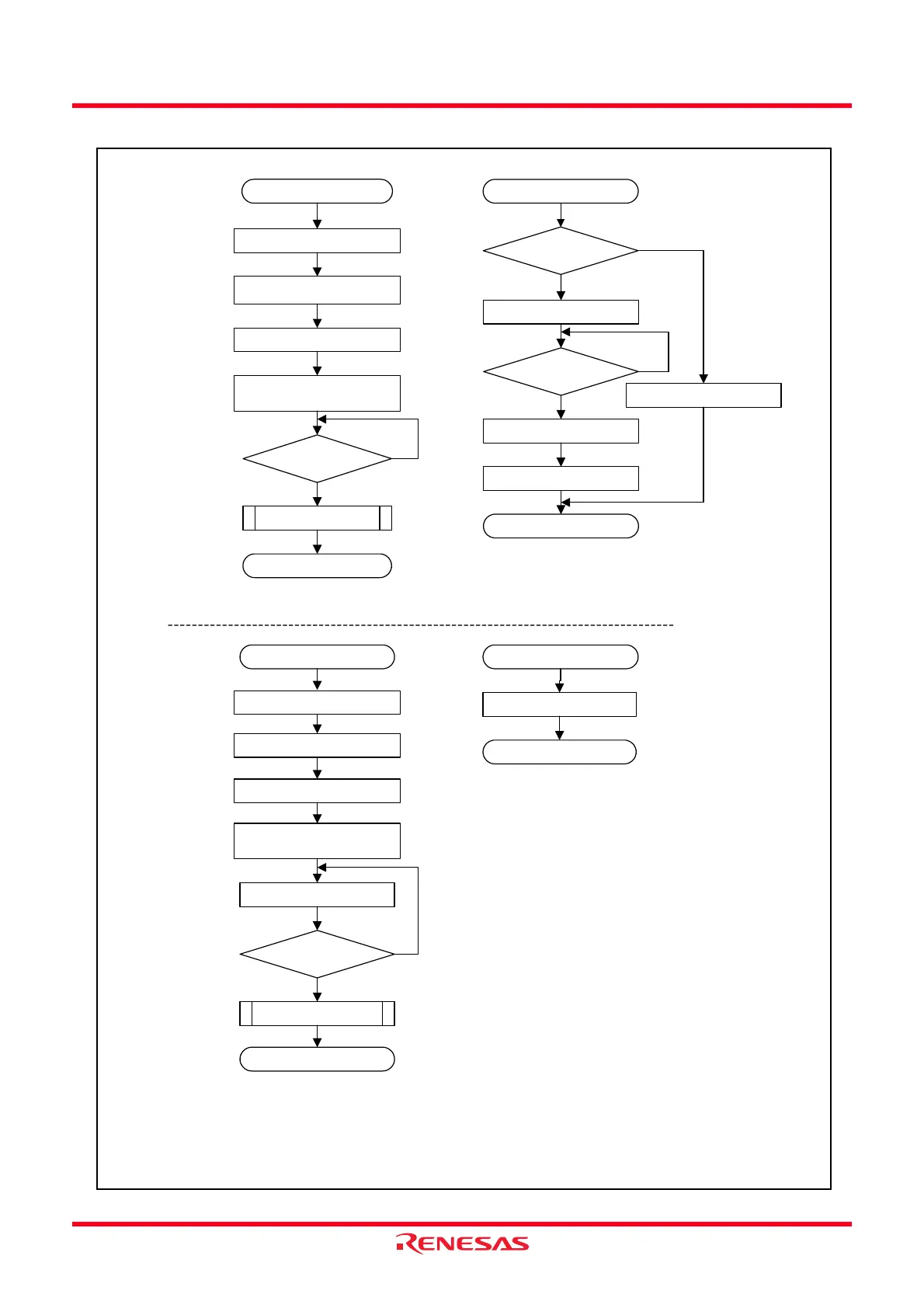

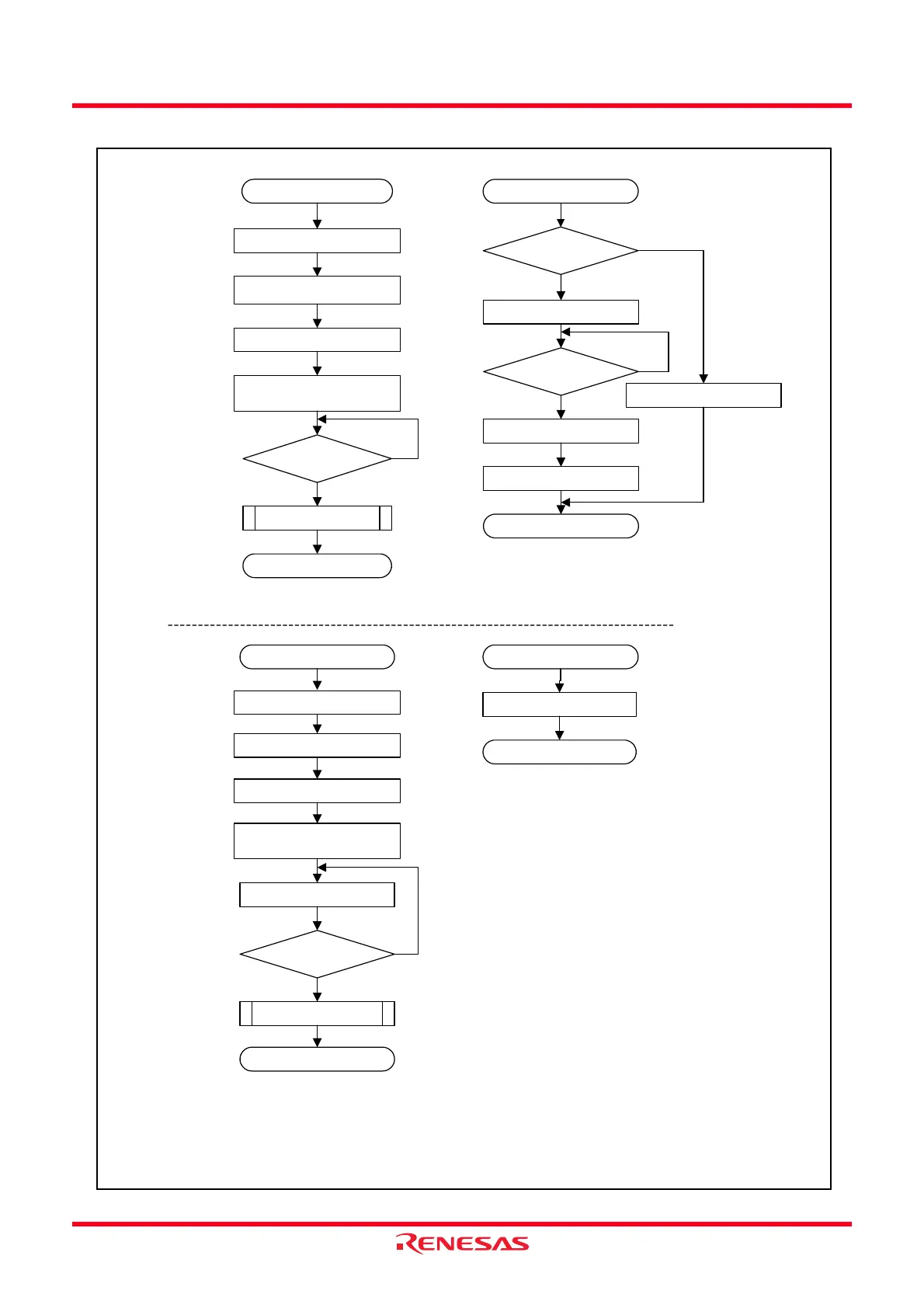

Figure 19.15 Block Erase Command (When Erase-Suspend Function Enabled)

Start

Write the command code 20h

Write D0h to any block

address

FMR00 = 1 ?

Full status check

Block erase completed

No

Yes

EW0 Mode

FMR40 = 1

Start

Write the command code 20h

Write D0h to any block

address

FMR00 = 1 ?

Full status check

Block erase completed

No

Yes

EW1 Mode

I = 1 (enable interrupt)

Maskable interrupt

(2)

REIT

Access flash memory

FMR41 = 0

NOTES:

1.In EW0 mode, the interrupt vector table and interrupt routine for interrupts to be used should be allocated to the RAM area.

2. td(SR-SUS) is needed until the interrupt request is acknowledged after it is generated. The interrupt to enter suspend

should be in interrupt enabled status.

3.When no interrupt is used, the instruction to enable interrupts is not needed.

4. td(SR-SUS) is needed until erase is suspended after the FMR41 bit in the FMR4 register is set to 1.

Maskable interrupt

(1)

FMR46 = 1 ?

REIT

Yes

FMR41 = 1

(4)

FMR41 = 0

Access flash memory

FMR43 = 1 ?

Yes

No

Access flash memory

No

I = 1 (enable interrupt)

(3)

FMR40 = 1

Loading...

Loading...