R8C/20 Group, R8C/21 Group 9. Bus

Rev.2.00 Aug 27, 2008 Page 63 of 458

REJ09B0250-0200

9. Bus

The bus cycles differ when accessing ROM/RAM, and when accessing SFR.

Table 9.1 lists Bus Cycles by Access Space of the R8C/20 Group and Table 9.2 lists Bus Cycles by Access Space of

the R8C/21 Group.

The ROM/RAM and SFR are connected to the CPU through an 8-bit bus. When accessing in word-(16 bits) unit, these

area are accessed twice in 8-bit unit.

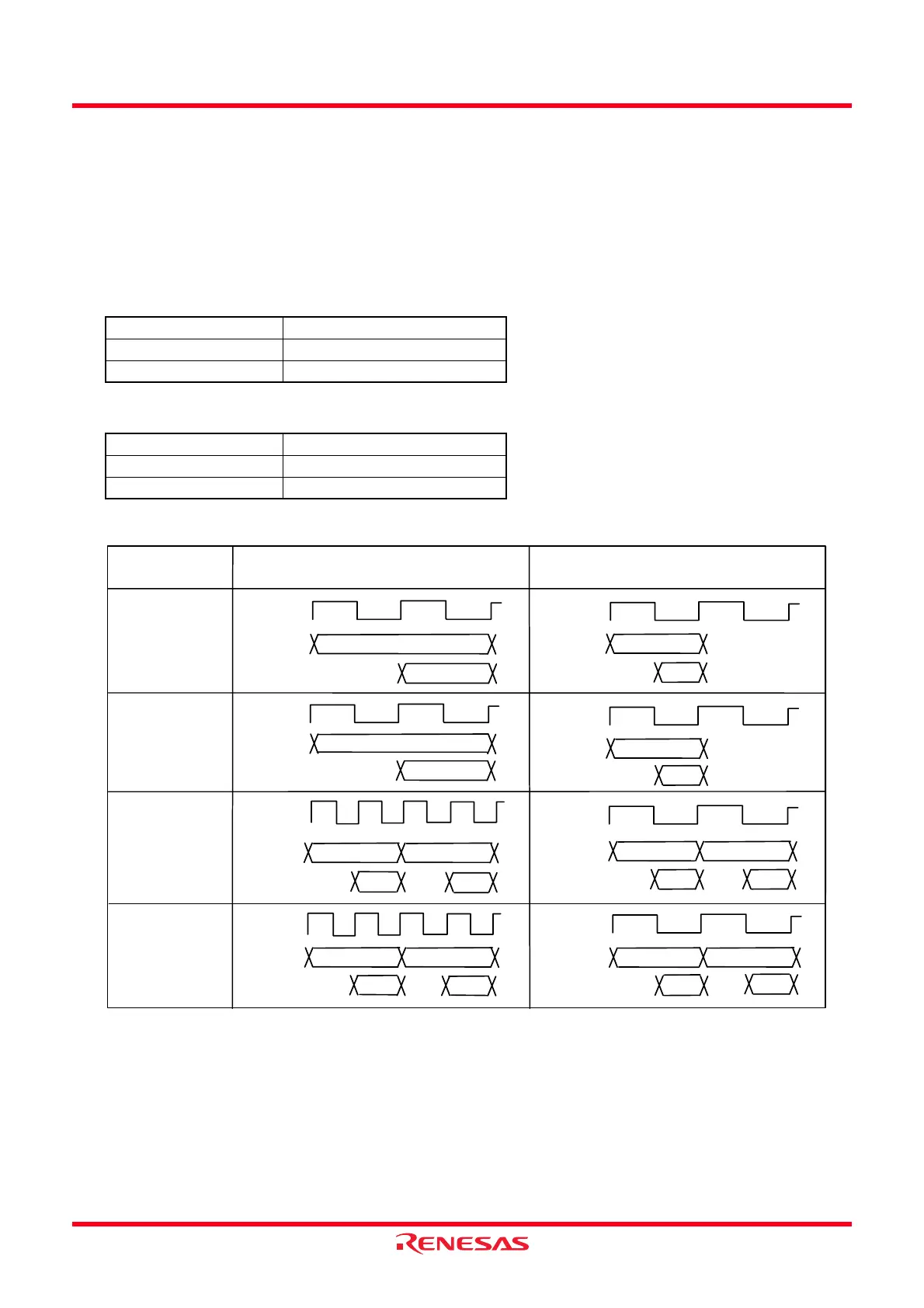

Table 9.3 lists Access Unit and Bus Operations.

Table 9.3 Access Unit and Bus Operations

However, only following SFRs are connected with the 16-bit bus:

Timer RD: registers TRDi (i = 0, 1), TRDGRAi, TRDGRBi, TRDGRCi, and TRDGRDi

Therefore, they are accessed once in 16-bit units. The bus operation is the same as “Area: SFR, data flash, even address

byte access” in Table 9.3 Access Unit and Bus Operations, and 16-bit data is accessed at a time.

Table 9.1 Bus Cycles by Access Space of the R8C/20 Group

Access Area Bus Cycle

SFR 2 cycles of CPU clock

ROM/RAM 1 cycle of CPU clock

Table 9.2 Bus Cycles by Access Space of the R8C/21 Group

Access Area Bus Cycle

SFR/Data flash 2 cycles of CPU clock

Program ROM/RAM 1 cycle of CPU clock

Area

SFR, data flash

Even address

byte access

ROM (program ROM), RAM

Odd address

byte access

Even address

word access

Odd address

word access

CPU clock

Data

Data

Data

Data

Data

Data

Data

Data

Data

Even

Even

Odd

Odd

Even + 1Even

Odd + 1Odd

Address

Even + 1

Odd + 1

Odd

Data

Data

Even

Data

CPU clock

Data

Address

CPU clock

Data

Address

CPU clock

Data

Address

Data

CPU clock

Address

Data

CPU clock

Address

Data

CPU clock

Address

Data

CPU clock

Address

Data

Loading...

Loading...