www.ti.com

J721E EVM Hardware Architecture

77

SPRUIS4A–December 2019–Revised May 2020

Submit Documentation Feedback

Copyright © 2019–2020, Texas Instruments Incorporated

Jacinto7 J721E/DRA829/TDA4VM Evaluation Module (EVM)

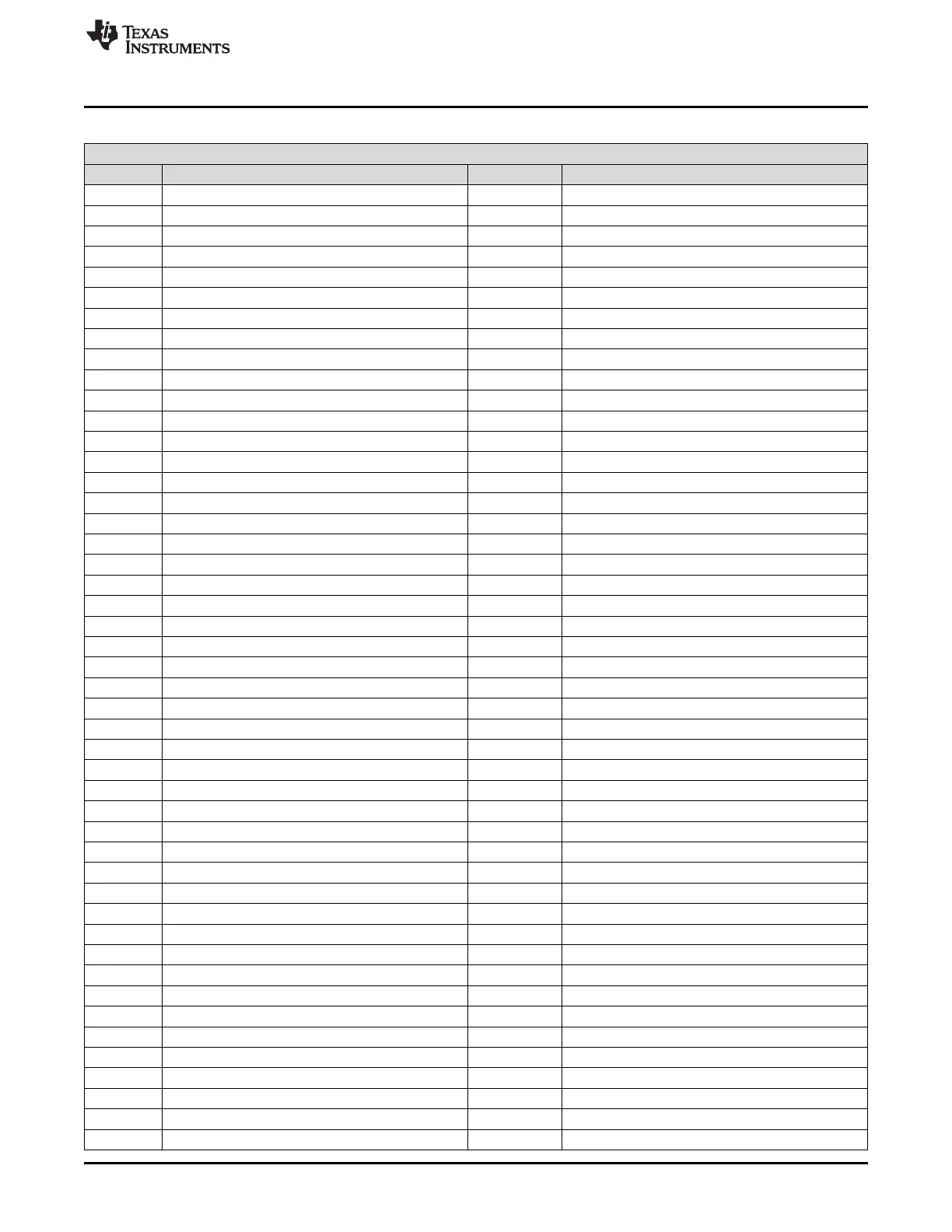

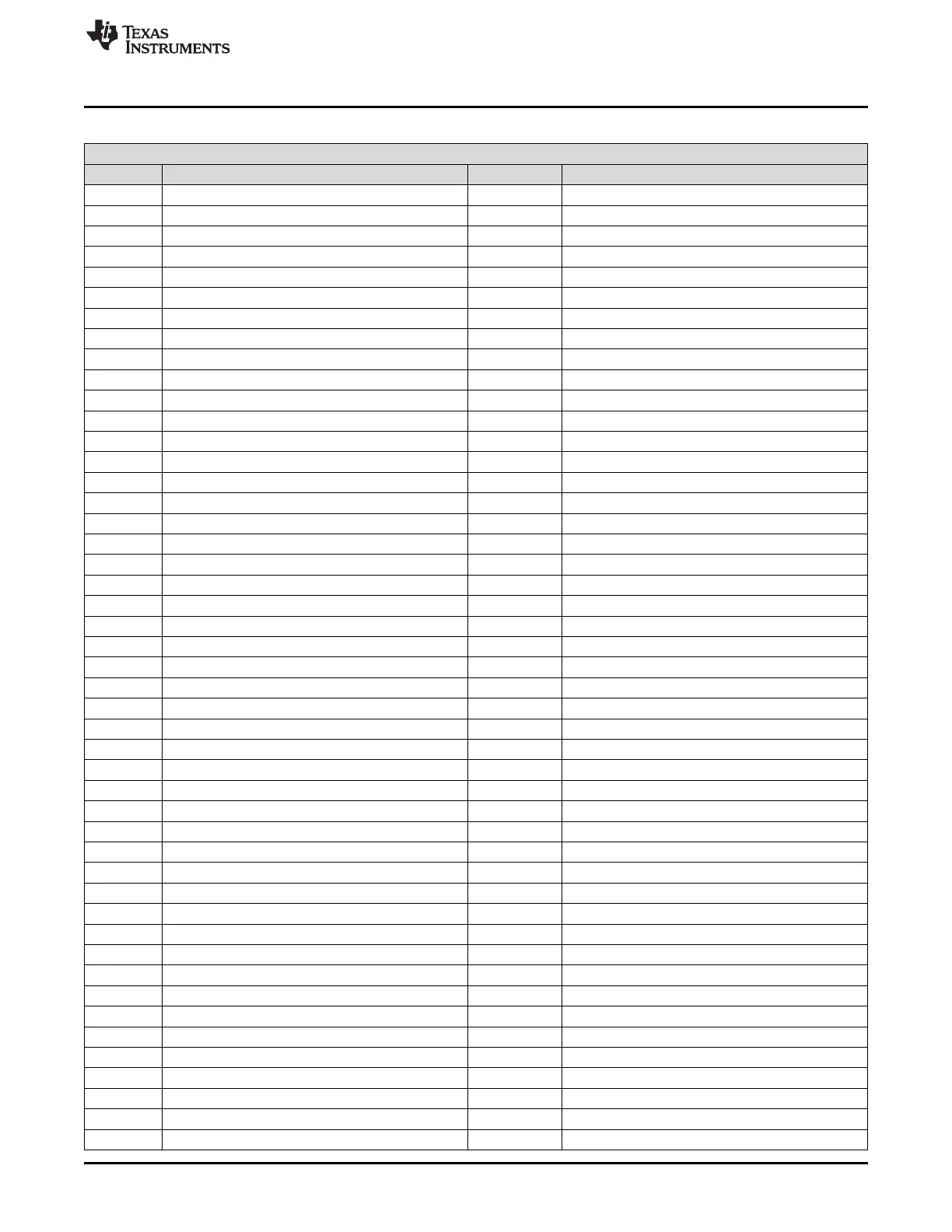

Table 45. EVM Expansion Connector J51 Pinout

INFO/GESI Connector Interface J51

Pin No Signal Pin No Signal

1 DGND 2 EXP_3V3

3 DGND 4 EXP_3V3

5 DGND 6 EXP_3V3

7 MCASP1_AXR5/UART8_RXD 8 I2C3_SCL

9 MCASP1_AXR6/UART8_TXD 10 I2C3_SDA

11 EQEP0_A 12 EQEP0_I

13 EQEP0_B 14 EQEP0_S

15 GPIO1_23/UART9_RXD 16 EXP_CODEC_SCKI

17 GPIO1_24/UART9_TXD 18 NC

19 EXP_EEPROM_A0 20 INFO_CAM_VIO_SEL

21 EXP_EEPROM_A1 22 EXP_REFCLK

23 EXP_EEPROM_A2 24 NC

25 BOARDID_EEPROM_WP 26 PRG1_IEP0_EDIO_OUTVALID

27 GPIO0_6 28 PERIPH_RSTz

29 GPIO0_61 30 RESETSTATz

31 UB926_GPIO2 32 EXP_MUX1

33 UB926_GPIO3 34 EXP_MUX2

35 NC 36 EXP_MUX3

37 NC 38 NC

39 DGND 40 DGND

41 GPMC0_A1 42 GPMC0_A22

43 GPMC0_A2 44 GPMC0_DIR

45 GPMC0_A3 46 GPMC0_A17

47 GPMC0_A4 48 GPMC0_BE1#

49 GPMC0_A5 50 GPMC0_A16

51 GPMC0_A7 52 GPMC0_A21

53 GPMC0_A6 54 GPMC0_A15

55 GPMC0_A9 56 GPMC0_A20

57 GPMC0_A11 58 GPMC0_A14

59 GPMC0_A8 60 GPMC0_A18

61 GPMC0_A10 62 GPMC0_A19

63 GPMC0_A12 64 GPMC0_A13

65 NC 66 NC

67 DGND 68 DGND

69 NC 70 NC

71 NC 72 NC

73 NC 74 NC

75 NC 76 NC

77 DGND 78 VSYS_5V0

79 DGND 80 VSYS_5V0

81 DGND 82 VSYS_5V0

83 MCU_ADC1_AIN0 84 NC

85 MCU_ADC1_AIN1 86 NC

87 MCU_ADC1_AIN2 88 NC

89 MCU_ADC1_AIN3 90 NC

91 MCU_ADC1_AIN4 92 NC

93 MCU_ADC1_AIN5 94 NC

Loading...

Loading...