49

TMS570LS0714

www.ti.com

SPNS226E –JUNE 2013–REVISED NOVEMBER 2016

Submit Documentation Feedback

Product Folder Links: TMS570LS0714

System Information and Electrical SpecificationsCopyright © 2013–2016, Texas Instruments Incorporated

6.5.6 CPU Self-Test

The CPU STC (Self-Test Controller) is used to test the two Cortex-R4F CPU Cores using the

Deterministic Logic BIST Controller as the test engine.

The main features of the self-test controller are:

• Ability to divide the complete test run into independent test intervals

• Capable of running the complete test as well as running few intervals at a time

• Ability to continue from the last executed interval (test set) as well as ability to restart from the

beginning (First test set)

• Complete isolation of the self-tested CPU core from rest of the system during the self-test run

• Ability to capture the Failure interval number

• Time-out counter for the CPU self-test run as a fail-safe feature

6.5.6.1 Application Sequence for CPU Self-Test

1. Configure clock domain frequencies.

2. Select number of test intervals to be run.

3. Configure the time-out period for the self-test run.

4. Enable self-test.

5. Wait for CPU reset.

6. In the reset handler, read CPU self-test status to identify any failures.

7. Retrieve CPU state if required.

For more information see the device Technical Reference Manual.

6.5.6.2 CPU Self-Test Clock Configuration

The maximum clock rate for the self-test is HCLKmax/2. The STCCLK is divided down from the CPU

clock. This divider is configured by the STCCLKDIV register at address 0xFFFFE108.

For more information see the device-specific Technical Reference Manual.

6.5.6.3 CPU Self-Test Coverage

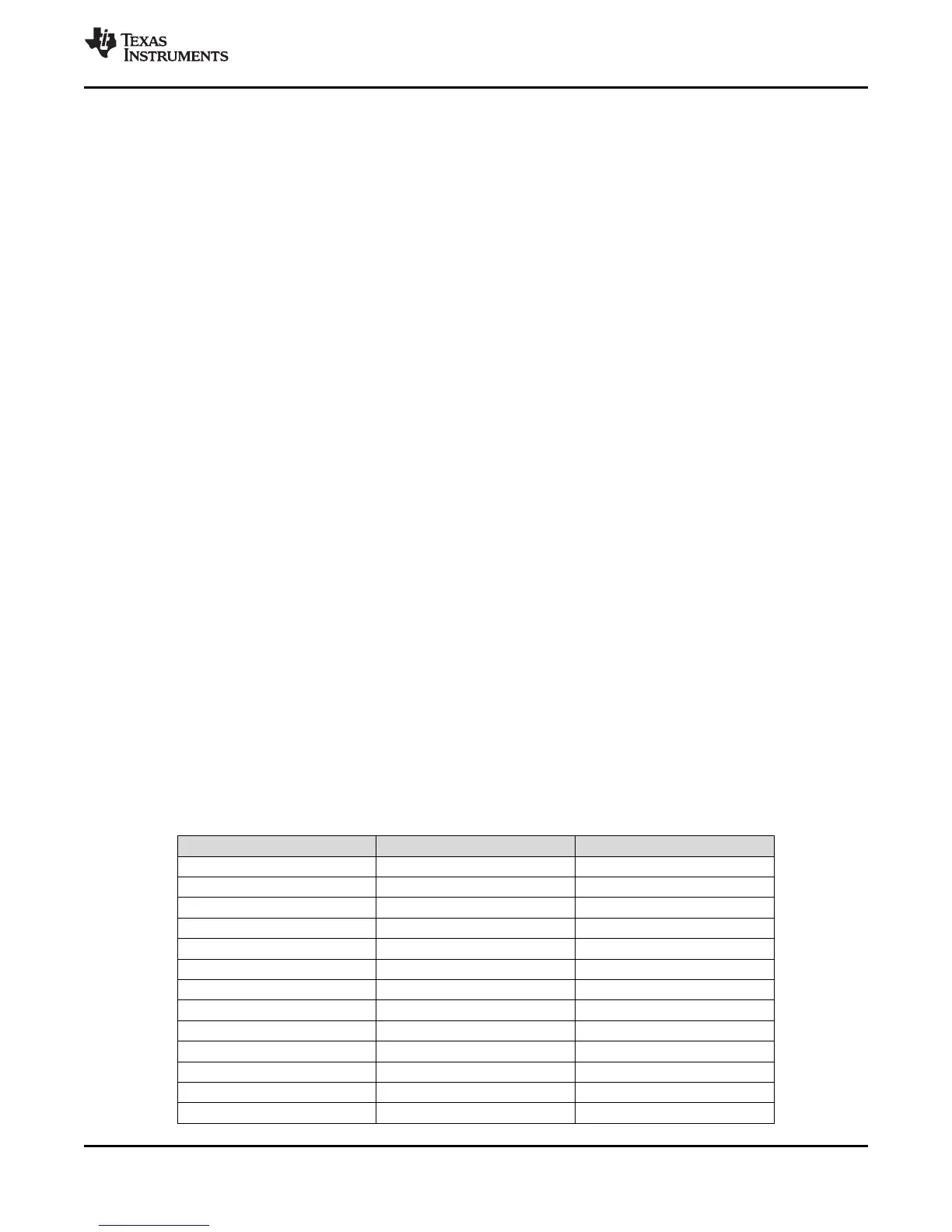

Table 6-7 lists the CPU self-test coverage achieved for each self-test interval. It also lists the cumulative

test cycles. The test time can be calculated by multiplying the number of test cycles with the STC clock

period.

Table 6-7. CPU Self-Test Coverage

INTERVALS TEST COVERAGE, % STCCLK CYLCES

0 0 0

1 62.13 1365

2 70.09 2730

3 74.49 4095

4 77.28 5460

5 79.28 6825

6 80.90 8190

7 82.02 9555

8 83.10 10920

9 84.08 12285

10 84.87 13650

11 85.59 15015

12 86.11 16380

Loading...

Loading...