44

TMS570LS0714

SPNS226E –JUNE 2013–REVISED NOVEMBER 2016

www.ti.com

Submit Documentation Feedback

Product Folder Links: TMS570LS0714

System Information and Electrical Specifications Copyright © 2013–2016, Texas Instruments Incorporated

6.2.3 Supply Filtering

The VMON has the capability to filter glitches on the VCC and VCCIO supplies.

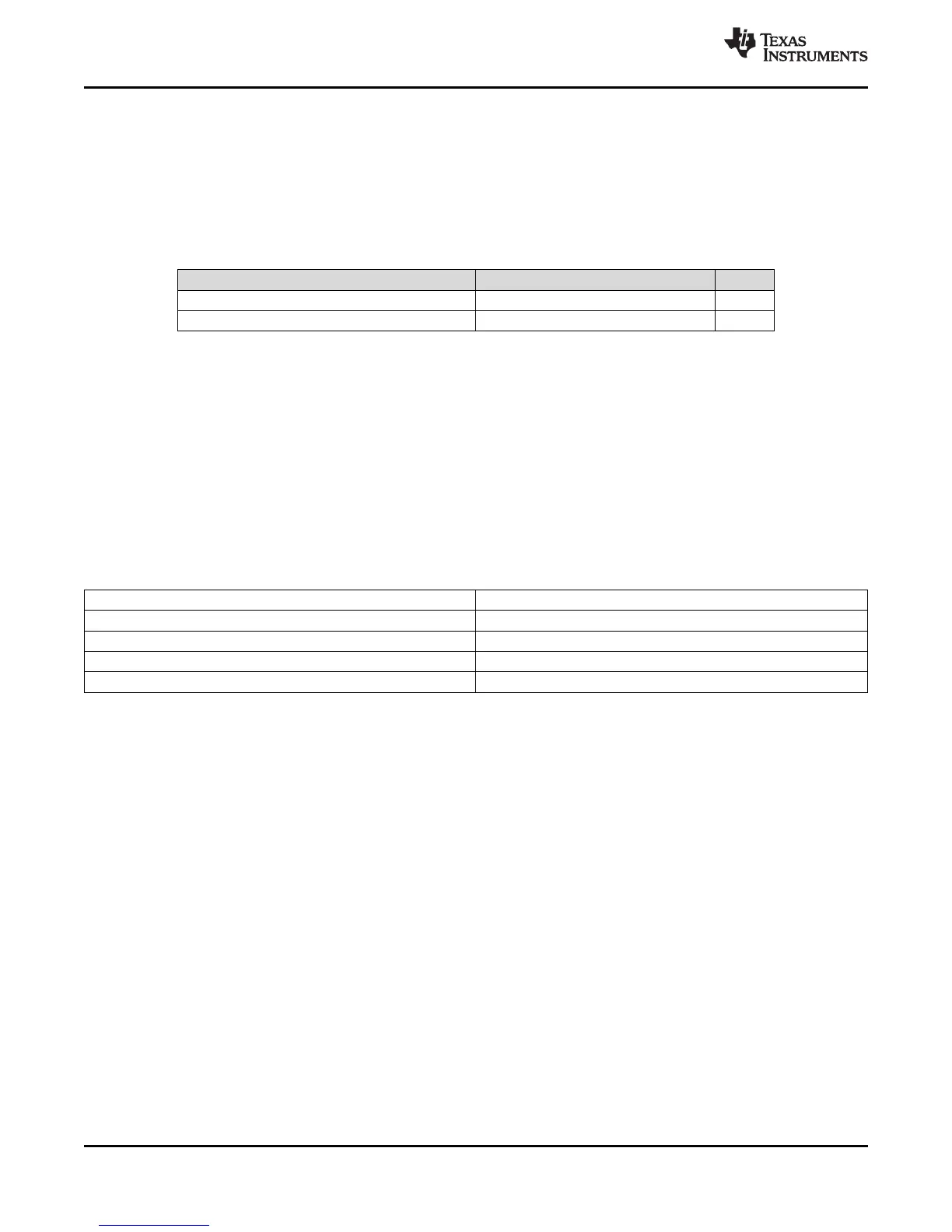

The following table shows the characteristics of the supply filtering. Glitches in the supply larger than the

maximum specification cannot be filtered.

Table 6-2. VMON Supply Glitch Filtering Capability

PARAMETER MIN MAX UNIT

Width of glitch on VCC that can be filtered 250 1000 ns

Width of glitch on VCCIO that can be filtered 250 1000 ns

6.3 Power Sequencing and Power-On Reset

6.3.1 Power-Up Sequence

There is no timing dependency between the ramp of the VCCIO and the VCC supply voltage. The power-

up sequence starts with the I/O voltage rising above the minimum I/O supply threshold, (see Table 6-4 for

more details), core voltage rising above the minimum core supply threshold and the release of power-on

reset. The high-frequency oscillator will start up first and its amplitude will grow to an acceptable level. The

oscillator start-up time is dependent on the type of oscillator and is provided by the oscillator vendor. The

different supplies to the device can be powered up in any order.

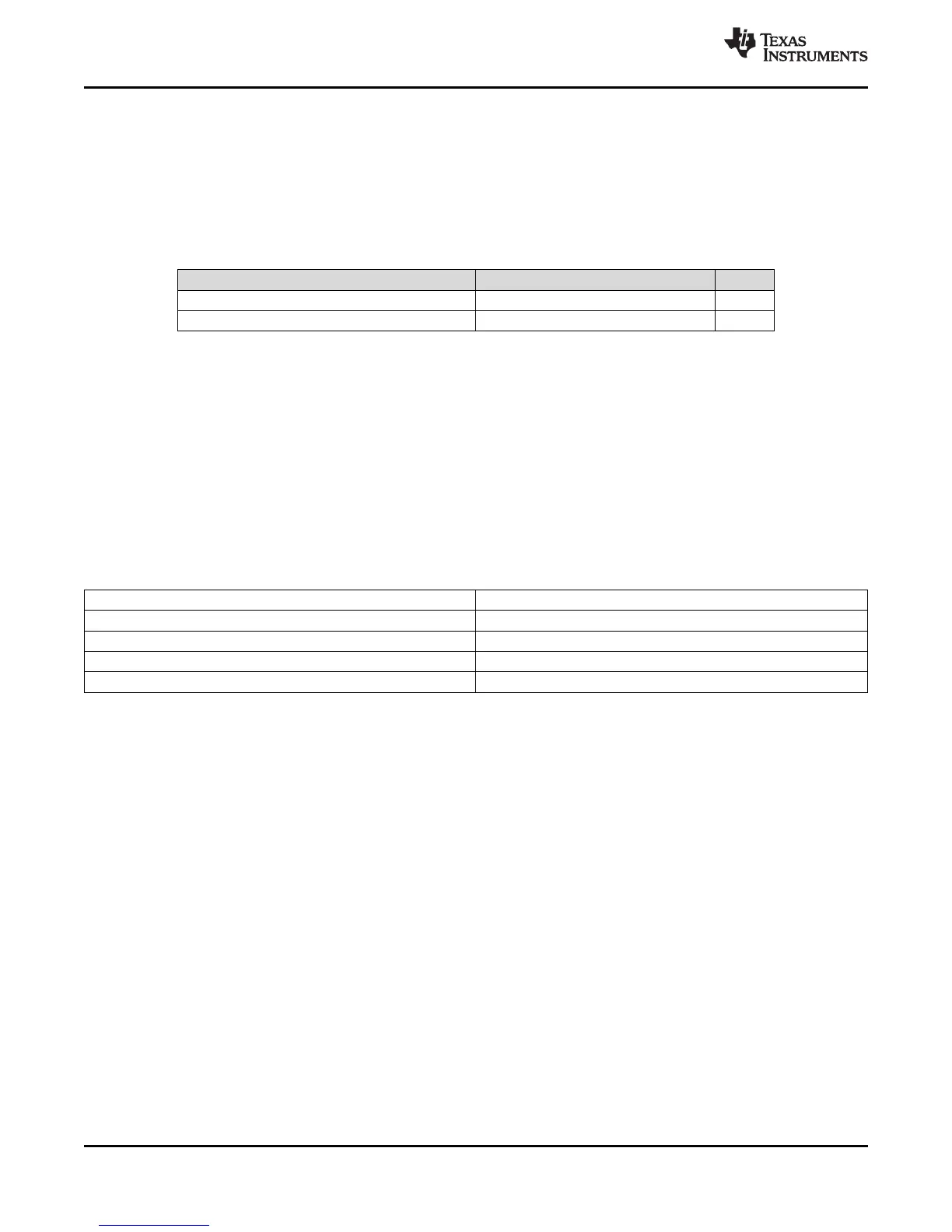

The device goes through the following sequential phases during power up.

Table 6-3. Power-Up Phases

Oscillator start-up and validity check 1032 oscillator cycles

eFuse autoload 1160 oscillator cycles

Flash pump power-up 688 oscillator cycles

Flash bank power-up 617 oscillator cycles

Total 3497 oscillator cycles

The CPU reset is released at the end of the above sequence and fetches the first instruction from address

0x00000000.

6.3.2 Power-Down Sequence

The different supplies to the device can be powered down in any order.

Loading...

Loading...