HTU1 HTU2

Switched Central Resource

Main Cross Bar: Arbitration and Prioritization Control

CRC

Peripheral Central Resource Bridge

Dual Cortex-R4F

CPUs in Lockstep

Switched Central Resource

DCAN1

DCAN2

DCAN3

LIN

SCI

SPI4

64KB Flash

for EEPROM

Emulation

with ECC

MibSPI1

CAN1_RX

CAN1_TX

CAN2_RX

CAN2_TX

CAN3_RX

CAN3_TX

MIBSPI1_CLK

MIBSPI1_SIMO[1:0]

MIBSPI1_SOMI[1:0]

MIBSPI1_nCS[5:0]

MIBSPI1_nENA

SPI2

SPI2_CLK

SPI2_SIMO

SPI2_SOMI

SPI2_nCS[1:0]

SPI2_nENA

MibSPI3

MIBSPI3_CLK

MIBSPI3_SIMO

MIBSPI3_SOMI

MIBSPI3_nCS[5:0]

MIBSPI3_nENA

SPI4_CLK

SPI4_SIMO

SPI4_SOMI

SPI4_nCS0

SPI4_nENA

MibSPI5

MIBSPI5_SIMO[3:0]

MIBSPI5_SOMI[3:0]

MIBSPI5_nCS[3:0]

MIBSPI5_nENA

LIN_RX

LIN_TX

SCI_RX

SCI_TX

IOMM

PMM

VIM

RTI

DCC1

DCC2

32K

32K

128KB

with ECC

RAM

DMA

# 2

# 3

# 5

# 1

# 1

always on

Core/RAM

RAM

Core

Color Legend for Power Domains

SYS

nPORRST

nRST

ECLK

ESM

nERROR

768KB

Flash

with

ECC

Switched Central Resource

I2C

N2HET1

GIO

I2C_SCL

I2C_SDA

GIOB[7:0]

GIOA[7:0]

N2HET2[18,16]

N2HET2[15:0]

N2HET1[31:0]

N2HET1_PIN_nDIS

N2HET2_PIN_nDIS

N2HET2

MibADC1 MibADC2

AD1EVT

AD1IN[7:0]

AD2EVT

VSSAD

VCCAD

ADREFHI

ADREFLO

AD1IN[15:8] \

AD2IN[15:8]

AD1IN[23:16] \

AD2IN[7:0]

eQEP

1,2

eQEPxA

eQEPxB

eQEPxS

eQEPxI

eCAP

1..6

eCAP[6:1]

ePWM

1..7

nTZ[3:1]

SYNCO

SYNCI

ePWMxA

ePWMxB

32K

32K

5

TMS570LS0714

www.ti.com

SPNS226E –JUNE 2013–REVISED NOVEMBER 2016

Submit Documentation Feedback

Product Folder Links: TMS570LS0714

Device OverviewCopyright © 2013–2016, Texas Instruments Incorporated

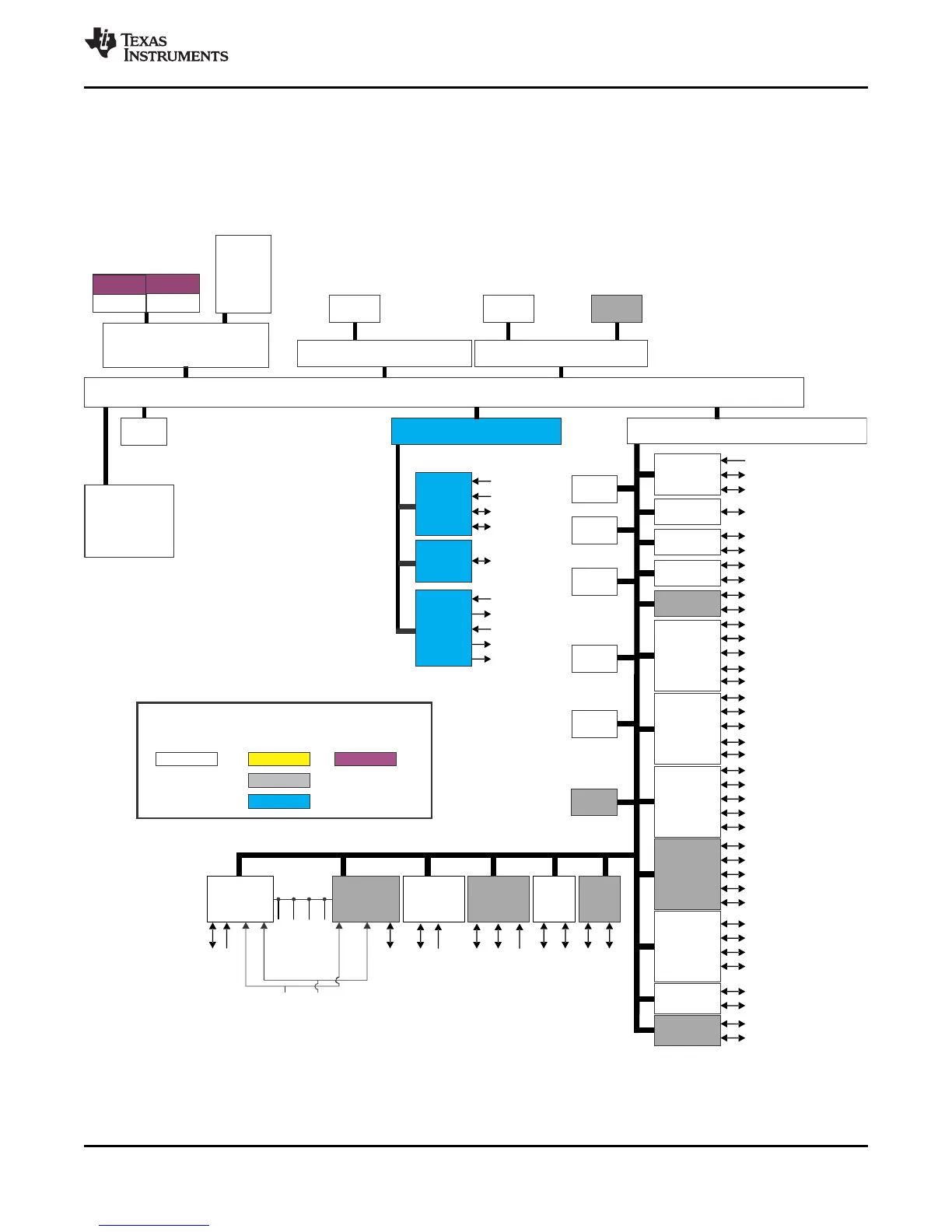

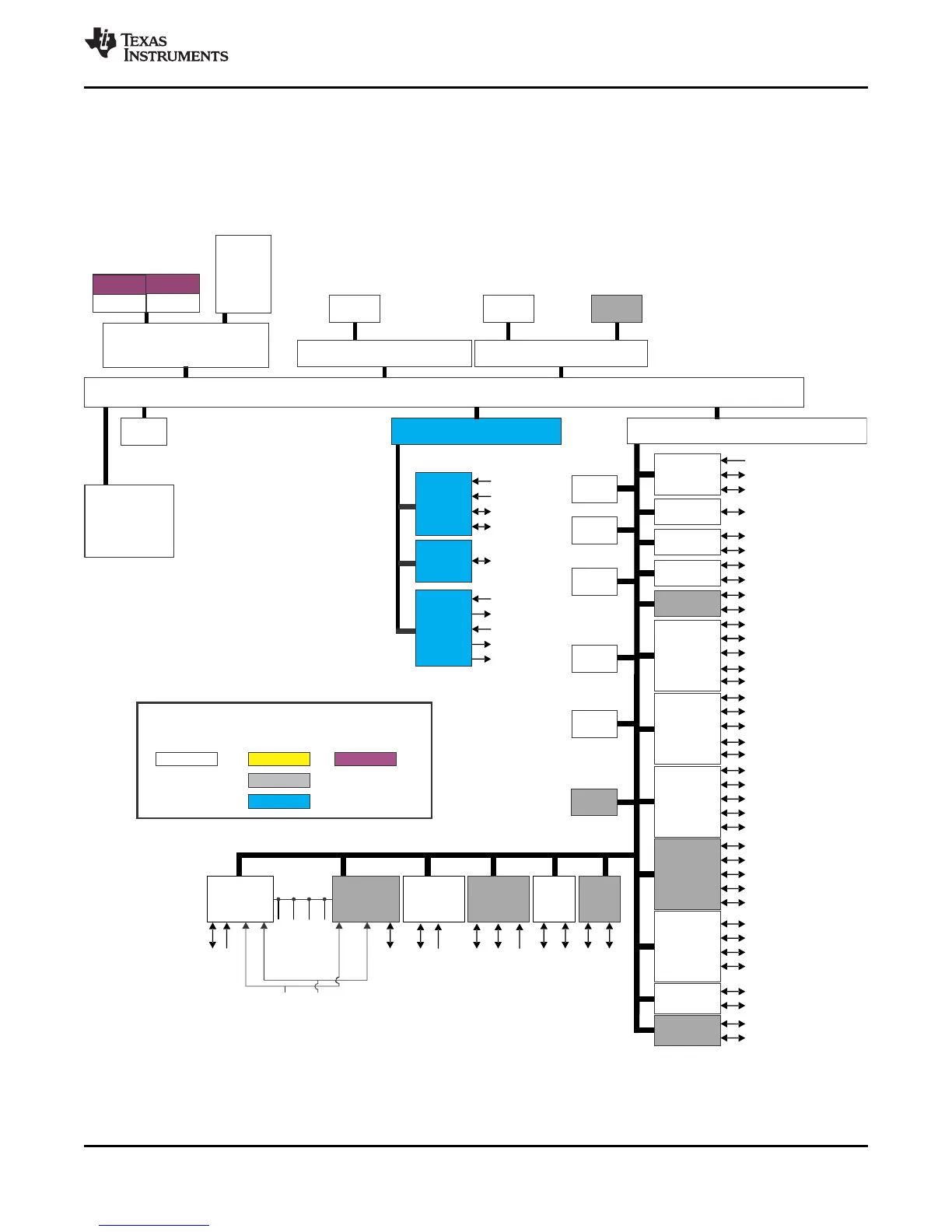

1.4 Functional Block Diagram

Figure 1-1 shows the functional block diagram of the device.

NOTE: The block diagram reflects the 144PGE package. Some functions are multiplexed or not available

in other packages. For details, see the respective terminal functions table in Section 4.2, Terminal

Functions.

Figure 1-1. Functional Block Diagram

Loading...

Loading...