71

TMS570LS0714

www.ti.com

SPNS226E –JUNE 2013–REVISED NOVEMBER 2016

Submit Documentation Feedback

Product Folder Links: TMS570LS0714

System Information and Electrical SpecificationsCopyright © 2013–2016, Texas Instruments Incorporated

(1) Several memory testing algorithms are stored in the PBIST ROM. However, TI recommends the March13N algorithm for application

testing of RAM.

(2) ESRAM1: Address 0x08000000 - 0x0800FFFF

(3) ESRAM5: Address 0x08010000 - 0x0801FFFF

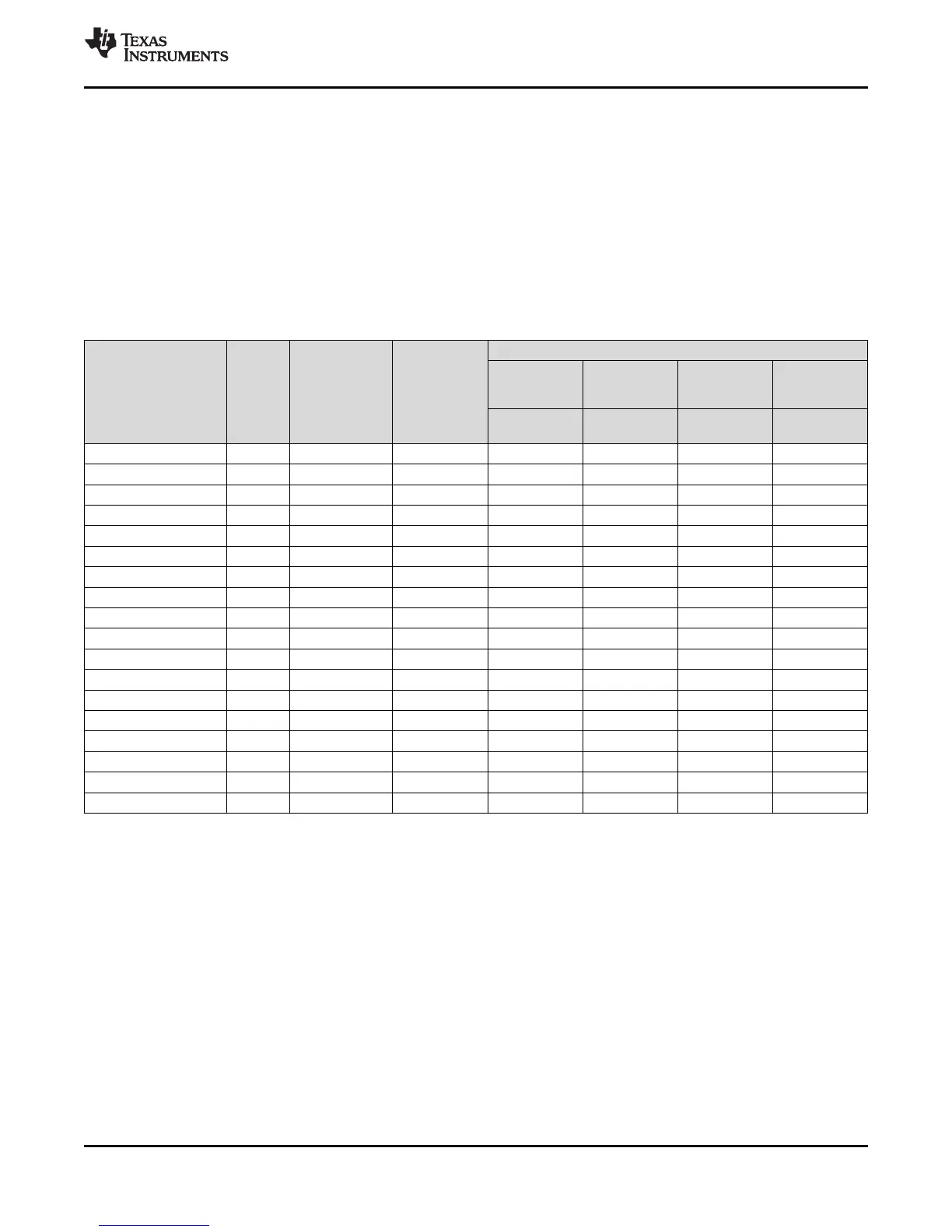

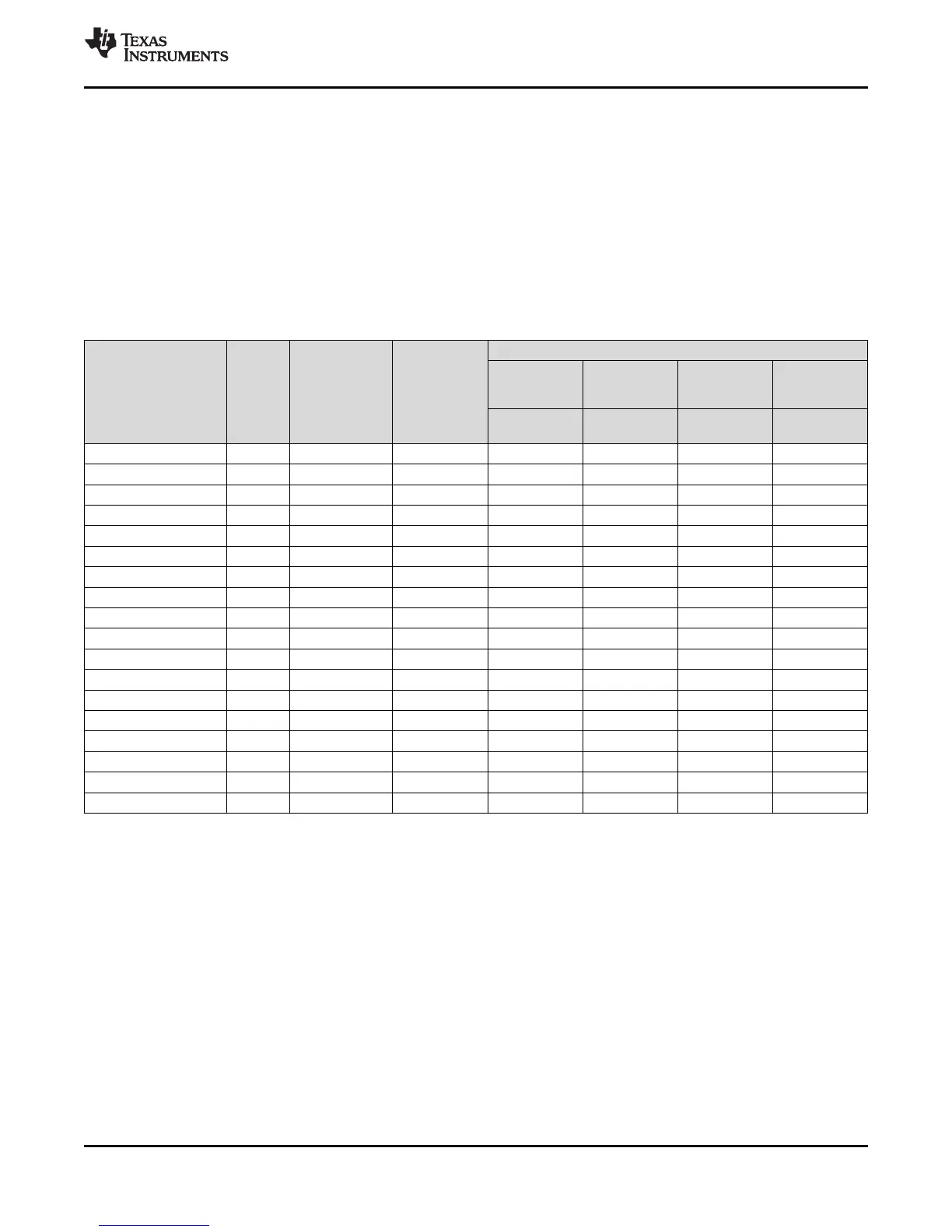

6.13 On-Chip SRAM Initialization and Testing

6.13.1 On-Chip SRAM Self-Test Using PBIST

6.13.1.1 Features

• Extensive instruction set to support various memory test algorithms

• ROM-based algorithms allow application to run TI production-level memory tests

• Independent testing of all on-chip SRAM

6.13.1.2 PBIST RAM Groups

Table 6-25. PBIST RAM Grouping

MEMORY

RAM

GROUP

TEST CLOCK

MEM

TYPE

Test Pattern (Algorithm)

TRIPLE READ

SLOW READ

TRIPLE READ

FAST READ

MARCH 13N

(1)

TWO PORT

(cycles)

MARCH 13N

(1)

SINGLE PORT

(cycles)

ALGO MASK

0x1

ALGO MASK

0x2

ALGO MASK

0x4

ALGO MASK

0x8

PBIST_ROM 1 ROM CLK ROM 24578 8194

STC_ROM 2 ROM CLK ROM 19586 6530

DCAN1 3 VCLK Dual port 25200

DCAN2 4 VCLK Dual port 25200

DCAN3 5 VCLK Dual port 25200

ESRAM1

(2)

6 HCLK Single port 266280

MIBSPI1 7 VCLK Dual port 33440

MIBSPI3 8 VCLK Dual port 33440

MIBSPI5 9 VCLK Dual port 33440

VIM 10 VCLK Dual port 12560

MIBADC1 11 VCLK Dual port 4200

DMA 12 HCLK Dual port 18960

N2HET1 13 VCLK Dual port 31680

HET TU1 14 VCLK Dual port 6480

MIBADC2 18 VCLK Dual port 4200

N2HET2 19 VCLK Dual port 31680

HET TU2 20 VCLK Dual port 6480

ESRAM5

(3)

21 HCLK Single port 266280

The PBIST ROM clock frequency is limited to 100 MHz, if 100 MHz < HCLK <= HCLKmax, or HCLK, if

HCLK <= 100 MHz.

The PBIST ROM clock is divided down from HCLK. The divider is selected by programming the ROM_DIV

field of the Memory Self-Test Global Control Register (MSTGCR) at address 0xFFFFFF58.

Loading...

Loading...