72

TMS570LS0714

SPNS226E –JUNE 2013–REVISED NOVEMBER 2016

www.ti.com

Submit Documentation Feedback

Product Folder Links: TMS570LS0714

System Information and Electrical Specifications Copyright © 2013–2016, Texas Instruments Incorporated

(1) The TCM RAM wrapper has separate control bits to select the RAM power domain that is to be auto-initialized.

(2) The MibSPIx modules perform an initialization of the transmit and receive RAMs as soon as the module is released from its local reset.

This is independent of whether the application chooses to initialize the MibSPIx RAMs using the system module auto-initialization

method. The MibSPIx module must be first brought out of its local reset to use the system module auto-initialization method.

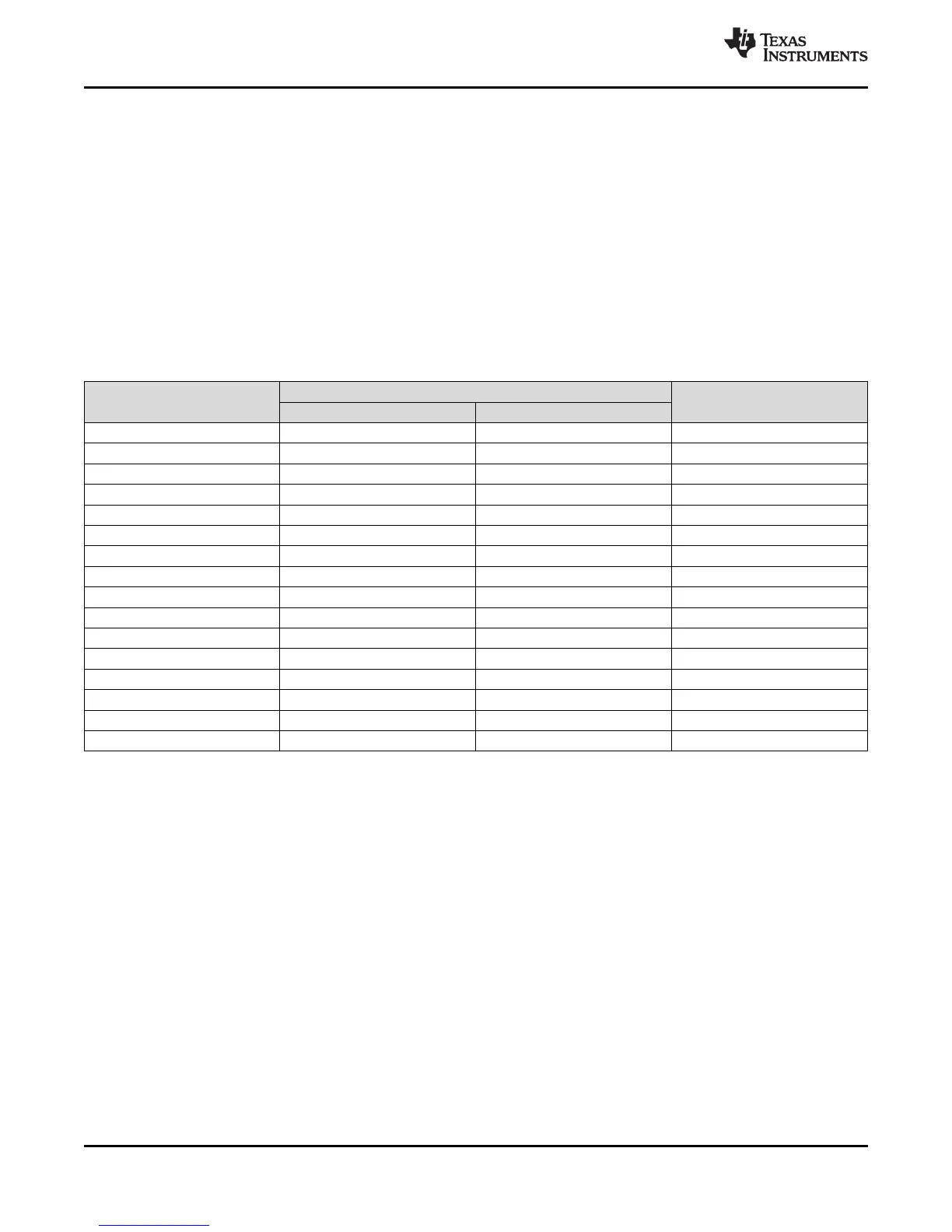

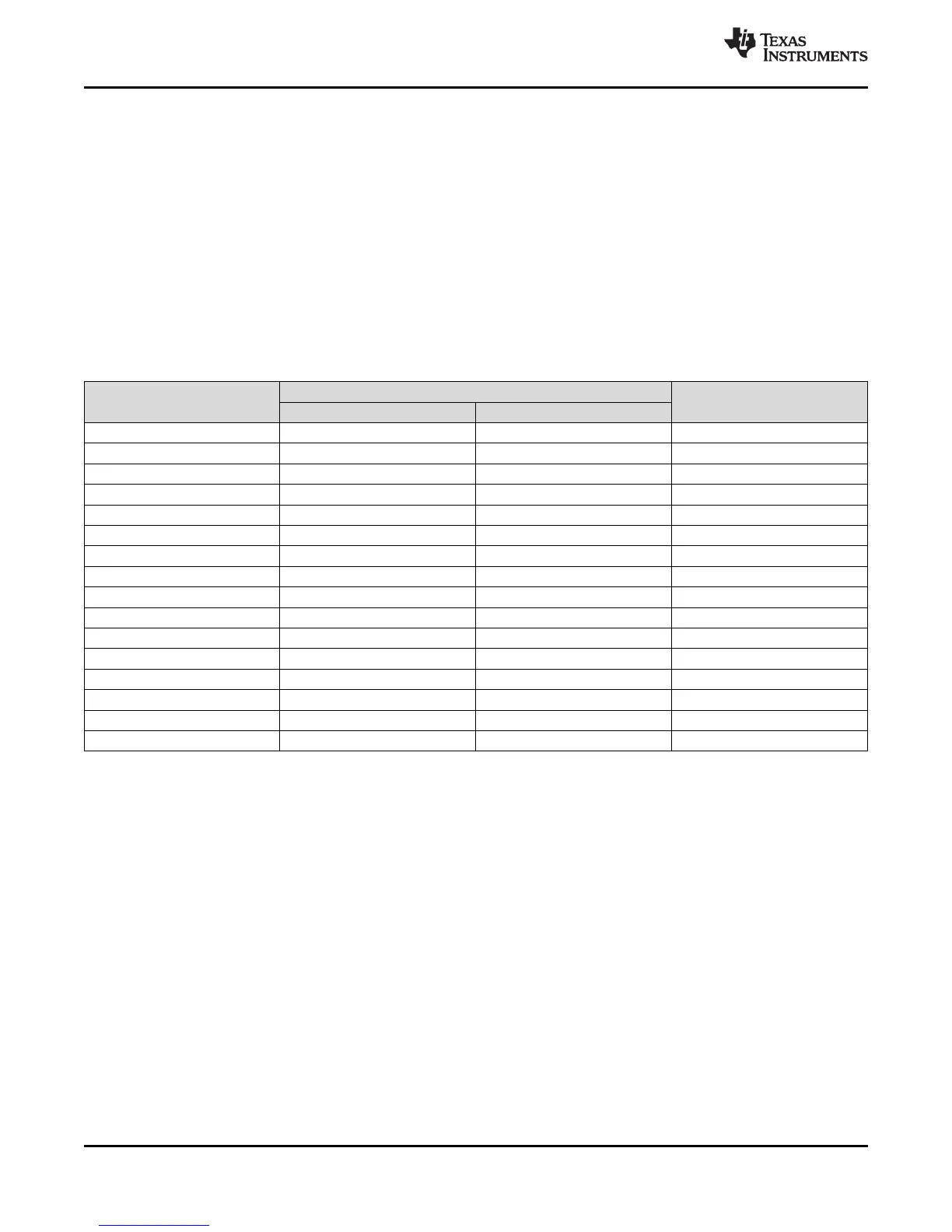

6.13.2 On-Chip SRAM Auto Initialization

This microcontroller allows some of the on-chip memories to be initialized through the Memory Hardware

Initialization mechanism in the system module. This hardware mechanism allows an application to

program the memory arrays with error detection capability to a known state based on their error detection

scheme (odd/even parity or ECC).

The MINITGCR register enables the memory initialization sequence, and the MSINENA register selects

the memories that are to be initialized.

For more information on these registers, see the device-specific Technical Reference Manual.

The mapping of the different on-chip memories to the specific bits of the MSINENA registers is shown in

Table 6-26.

Table 6-26. Memory Initialization

CONNECTING MODULE

ADDRESS RANGE

MSINENA REGISTER BIT #

BASE ADDRESS ENDING ADDRESS

RAM (PD#1) 0x08000000 0x0800FFFF 0

(1)

RAM (RAM_PD#1) 0x08010000 0x0801FFFF 0

(1)

MIBSPI5 RAM 0xFF0A0000 0xFF0BFFFF 12

(2)

MIBSPI3 RAM 0xFF0C0000 0xFF0DFFFF 11

(2)

MIBSPI1 RAM 0xFF0E0000 0xFF0FFFFF 7

(2)

DCAN3 RAM 0xFF1A0000 0xFF1BFFFF 10

DCAN2 RAM 0xFF1C0000 0xFF1DFFFF 6

DCAN1 RAM 0xFF1E0000 0xFF1FFFFF 5

MIBADC2 RAM 0xFF3A0000 0xFF3BFFFF 14

MIBADC1 RAM 0xFF3E0000 0xFF3FFFFF 8

N2HET2 RAM 0xFF440000 0xFF45FFFF 15

N2HET1 RAM 0xFF460000 0xFF47FFFF 3

HET TU2 RAM 0xFF4C0000 0xFF4DFFFF 16

HET TU1 RAM 0xFF4E0000 0xFF4FFFFF 4

DMA RAM 0xFFF80000 0xFFF80FFF 1

VIM RAM 0xFFF82000 0xFFF82FFF 2

Loading...

Loading...