USER’S MANUAL__________________________________________________________________

24 __________________________________________________________________ M211322EN-D

0916-005

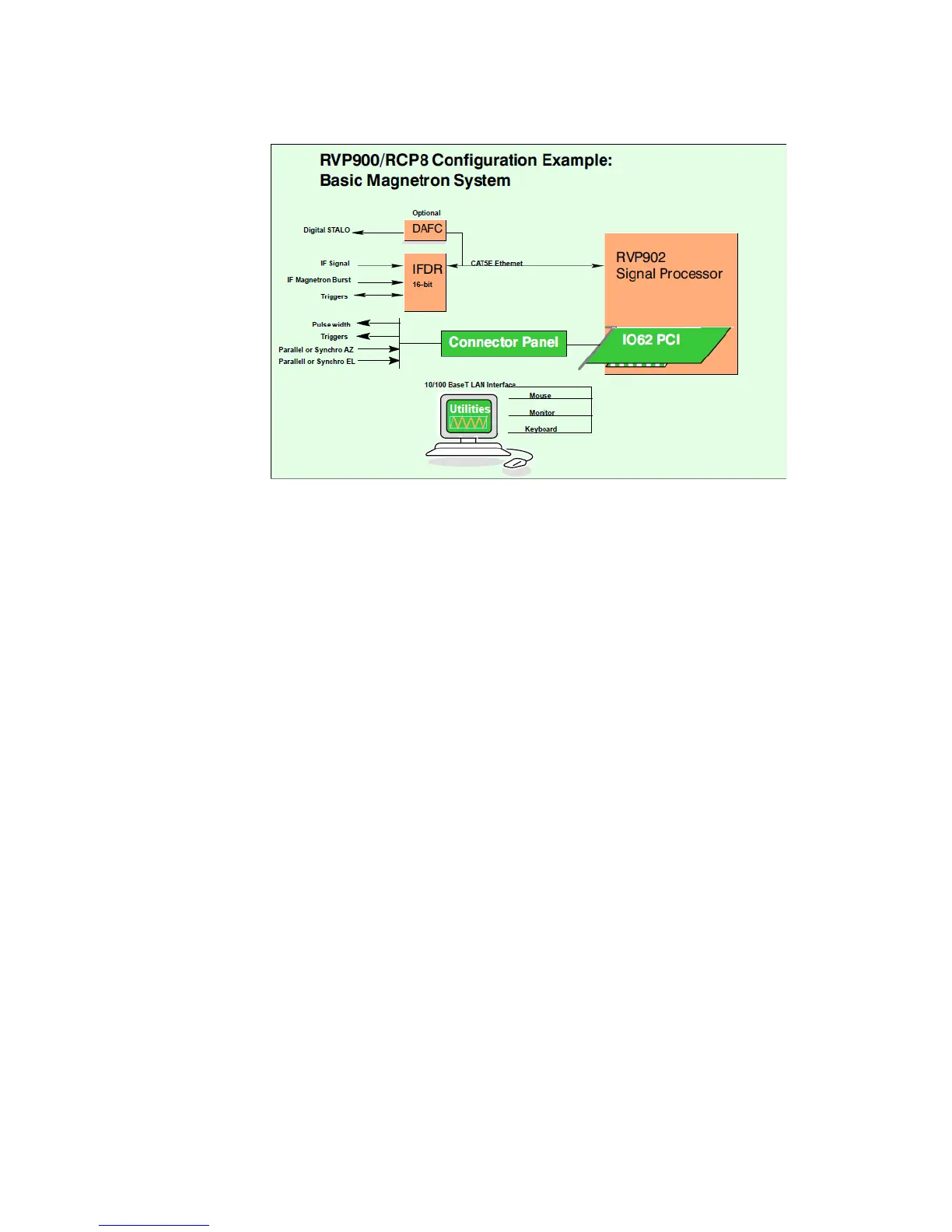

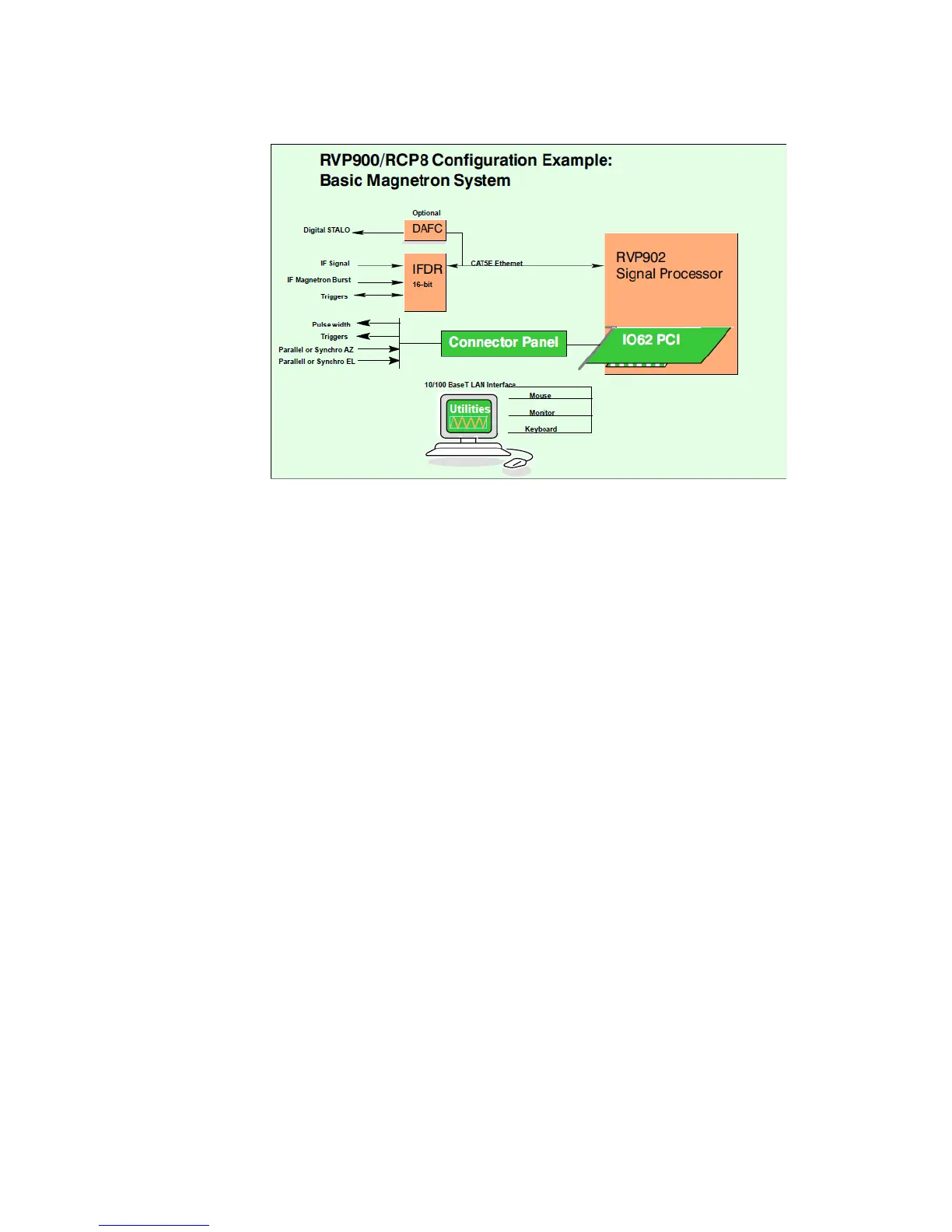

Figure 2 Example 1: Basic Magnetron System

The building blocks required to construct the basic system are:

- RVP901 IFDR—IDR installed in the radar receiver cabinet. This can

be located up to 25 m from the RVP902 main chassis. The Digital

Automatic Frequency Control (DAFC) is an option to interface to a

digitally controlled STALO. The RVP900 provides full AFC control

with burst pulse auto-tracking.

- I/O-62 PCI Card—This card is still available for additional triggers,

parallel, synchro or encoder AZ and EL angle inputs, pulse width

control, spot blanking control output, and more. These signals are

brought in through the connector panel.

- RVP902 Signal Processor—1U, 19 in, rack-mounted computer with

two quad-core Intel Xeon processors (PC) running a Linux operating

system.

Figure 2 shows a basic magnetron system. The RCP8 I/O-62 PCI card

continues to be used for generic input/output until the next generation of

back panel is developed. This system has approximately five times the

processing power of the fastest RVP8 ever produced (with dual 3.0 GHz

Pentium processors), so that it is capable of performing DFT processing in

4200 range bins with advanced algorithms such as random phase second

trip echo filtering and recovery.

Loading...

Loading...