Appendix B _______________________________________________________ RVP900 Packaging

VAISALA______________________________________________________________________ 355

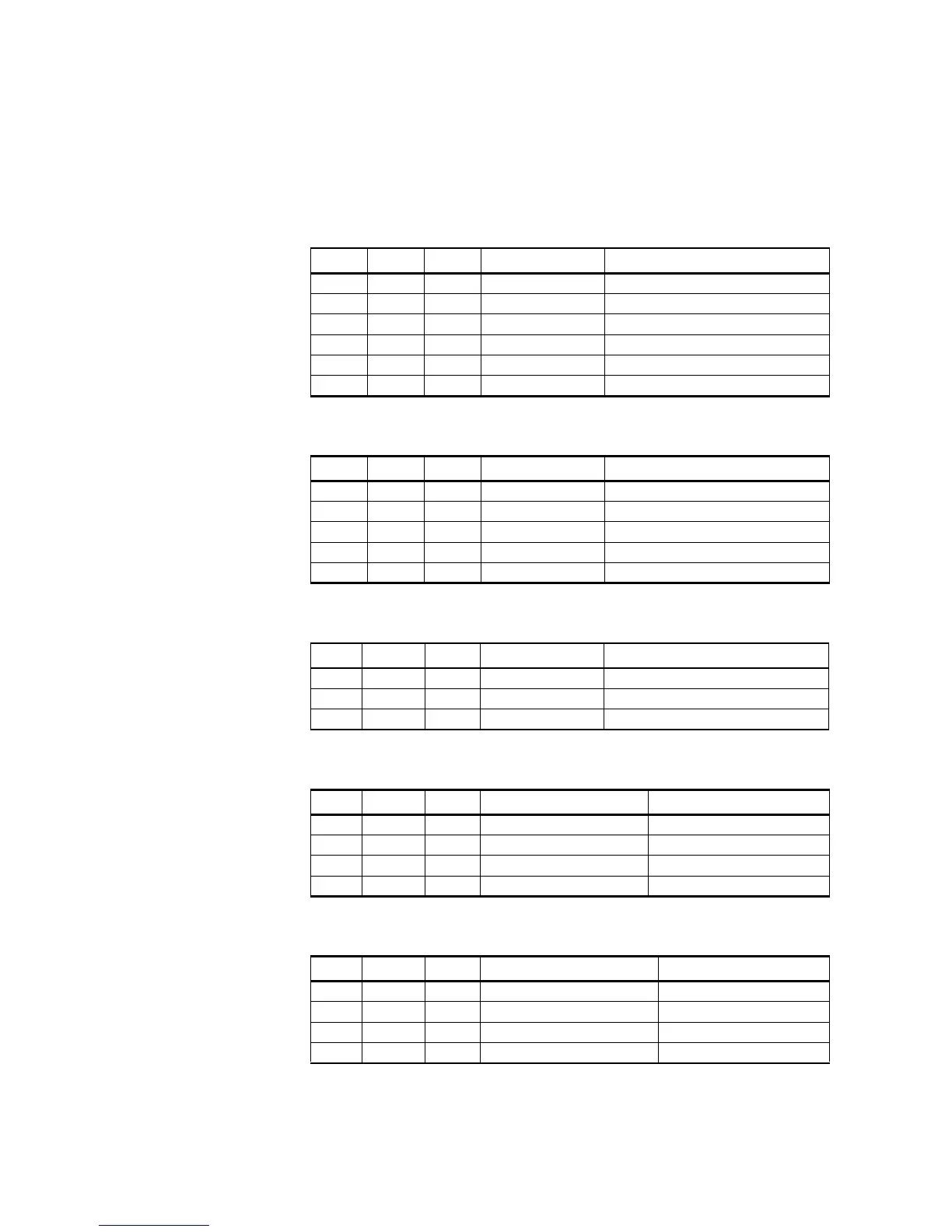

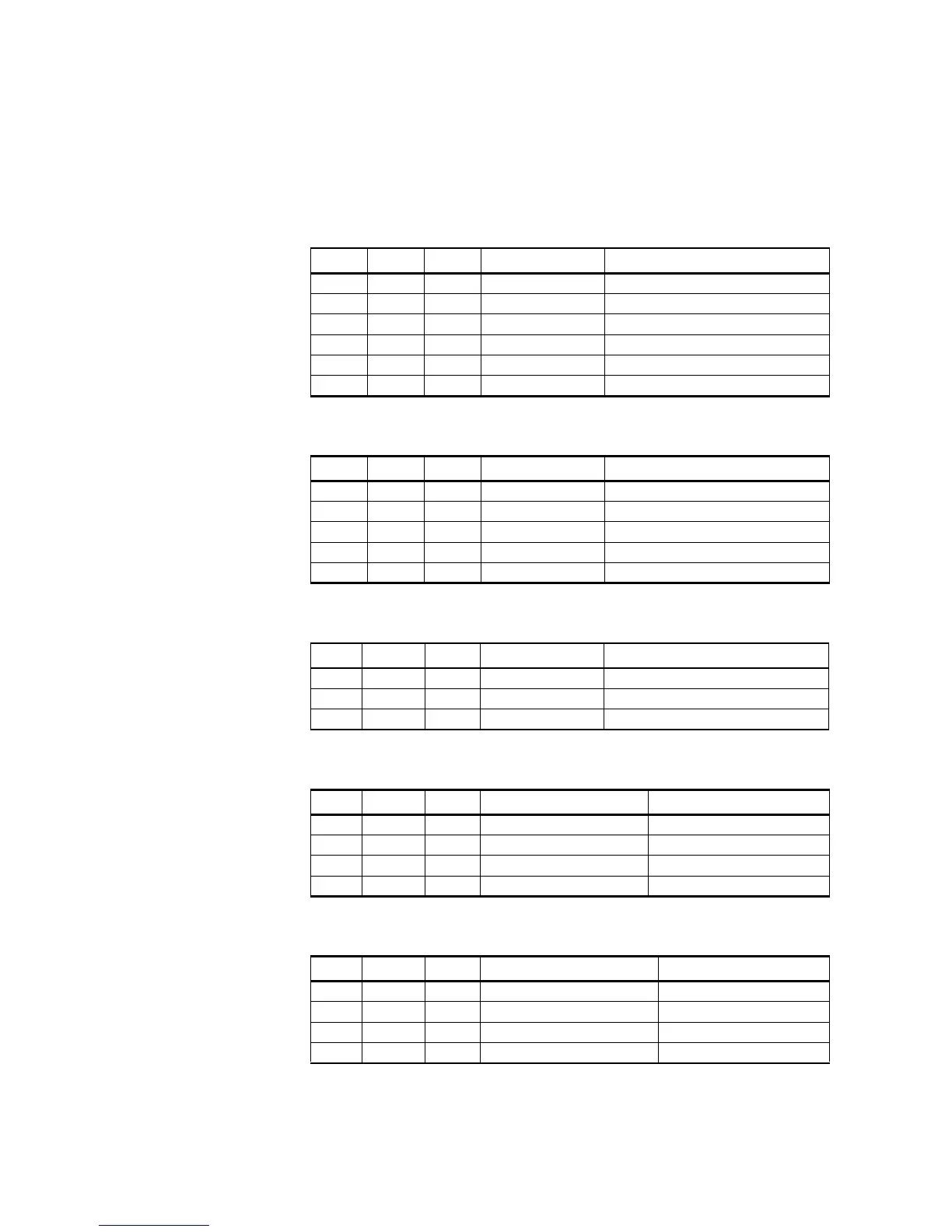

The signals assigned to the back panel’s 25-pin I/O connectors are shown

in Tables TBD to TBD. Each line in the tables generally describes a pair of

signals that should be twisted together for best signal integrity. A common

ground is provided on Pin-25 of all eight connectors.

Table 18 J1 “Filter Amp #1”

Pin Type Dir Signal Name Comment

1/14 TTL Out RFSW/GND Command, RF Upconvert Switch

2/15 TTL Out RFTST/GND Command, RF Test Switch

3/16 TTL Out RFTSTPP/GND Command, RF Pilot Pulse Switch

4/17 TTL Out RFTSTTER/GND Command, RF Test Term Switch

5/18 TTL In RFXTALFM/GND Status, Crystal Fault Monitor

25 — — GND Common Ground

Table 19 J2 “Filter Amp #2”

Pin Type Dir Signal Name Comment

2/15 TTL In MULTRF/GND Status, Multiplier Fault

3/16 TTL In RFLOFM/GND Status, RF LO Generator Fault

4/17 TTL In RFTSTFM/GND Status, RF Test Fault

5/18 TTL In RFFM/GND Status, RF Generator Fault

25 — — GND Common Ground

Table 20 J3 “Pedestal”

Pin Type Dir Signal Name Comment

3/16 RS-422 In ACP/ACPn Antenna Control Pulse

4/17 RS-422 In ARP/ARPn Antenna Reset Pulse

25 — — GND Common Ground

Table 21 J4 “Transmitter”

Pin Type Dir Signal Name Comment

4/17 RS-422 Out RFAMPGT/RFAMPGTn Transmitter Trigger

5/18 RS-422 Out BPIGT/BPIGTn Transmitter Trigger

6/19 RS-422 Out PFNGT/PFNGTn Transmitter Trigger

25 — — GND Common Ground

Table 22 J5 “STC #1”

Pin Type Dir Signal Name Comment

5/18 RS-422 Out STCTRG/STCTRGn STC Real–time Trigger

6/19 RS-422 Out STCCLK/STCCLK/n STC Real–time Clock

7/20 RS-422 Out STCBDCLK/STCBDCLKn STC Serial Loadup Clock

25 — — GND Common Ground

Loading...

Loading...