Chapter 3 _______________________________________________________ Hardware Installation

VAISALA_______________________________________________________________________ 95

the user has chosen, usually through the Pb and Ps plotting setup

commands.

Following the burst window is a fixed-length sequence of 25 serial data

bits, which convey information from the IFDR. The first four data bits

form a characteristic (0,1,1,0) marker pattern. The first zero in this pattern

effectively marks the end of the variable length burst window, and the

other three bits should be checked for added confidence that a valid bit

sequence is being received. Table 8 on page 93 provides the interpretation

of the serial data bits.

The period τ

s

of the serial data is (128/f

aq

) , where f

aq

is the acquisition

clock frequency given in the Mc section of the RVP900 setup menu. For

the default clock frequency of 71.9502 MHz, the period of the serial data

is 1.779 μsec. The logic that is receiving the serial data should first locate

the center of the first data bit at (0.5 × τ

s

) past the falling edge at the end of

the burst window. Subsequent data bits are then sampled at uniform τ

s

intervals.

The actual data sampling rate can be in error by as much as one part in 75

while still maintaining accurate reception. This is because the data

sequence is only 25-bits long, and therefore, the last data bit would still be

sampled within ±1/3 bit time of its center. Having this flexibility makes it

easier to design the receiving logic. For example, if a 5 MHz or 10 MHz

clock were available, then sampling at 1.8 µsec intervals (1:85 error)

would be fine. Similarly, one could sample at 1.75 µsec based on a 4 MHz

or 8 MHz clock (1:61 error), but only if the first sample were moved

slightly ahead of center, so that the sampling errors were equalized over the

25-bit span.

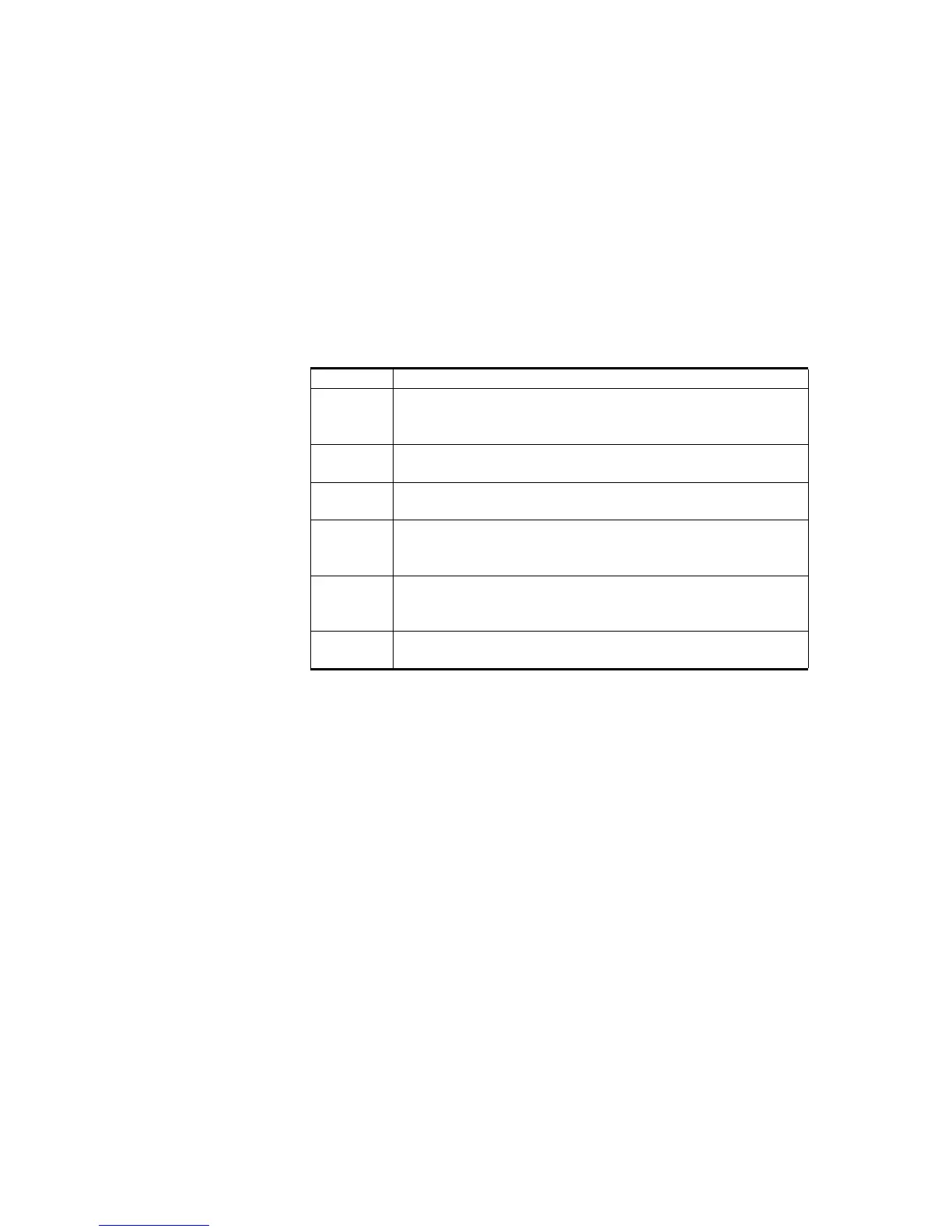

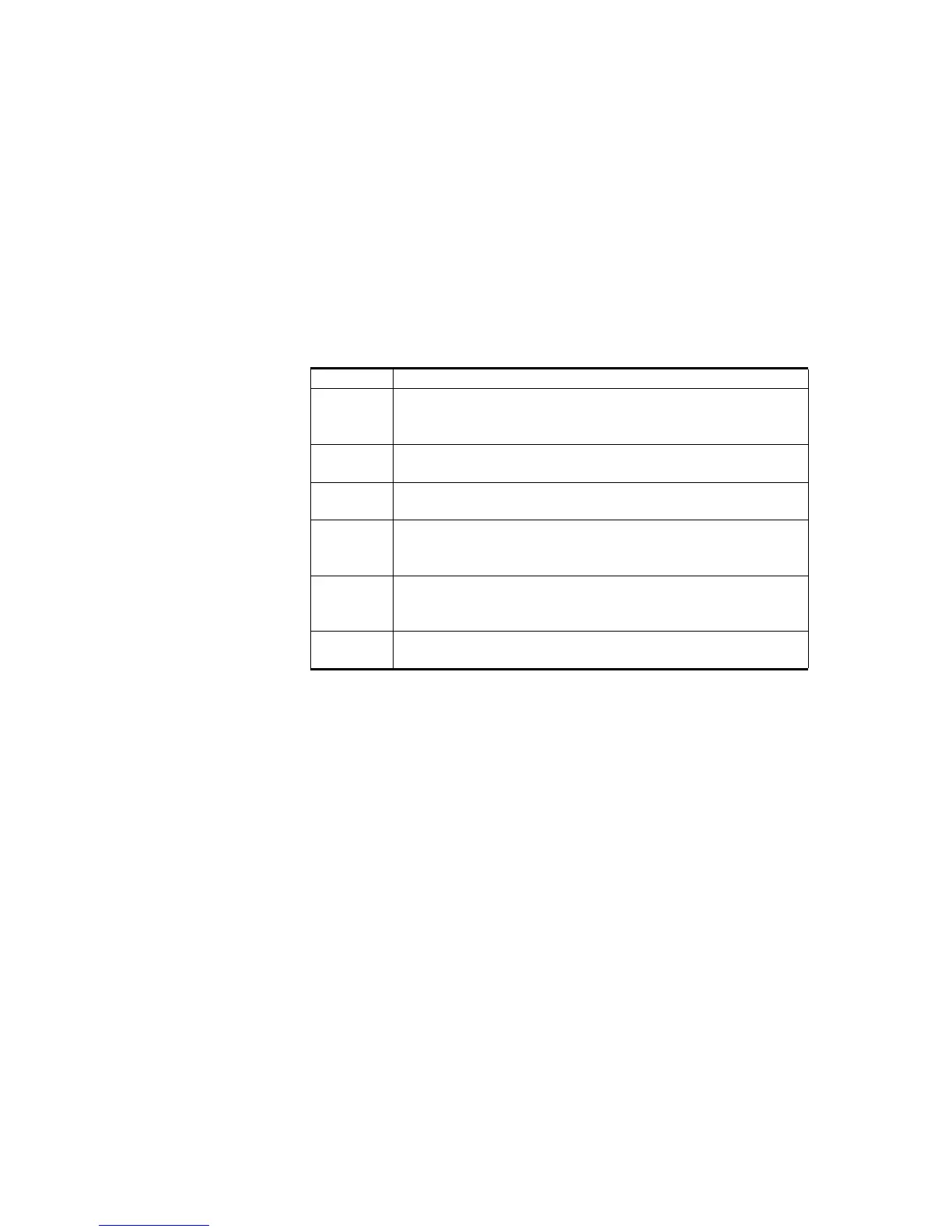

Table 8 Bit Assignments for the IFDR Coax Uplink

Bit(s) Meaning

1 to 4 Marker Sequence (0,1,1,0). This fixed, 4-bit sequence

identifies the start of a valid data sequence following the

variable-length burst window.

5 to 20 16-bit, multi-purpose data word, MSB is transmitted first (see

below)

21 Reset Request. This bit sets in just one transmitted sequence

whenever an RVP900 reset occurs.

22 If set, then interpret the 16-bit data word as 4-bits of command

and 12-bits of data, rather than as a single 16-bit quantity (see

below)

23 to 24 Diagnostic select bits. These are used by the RVP900 power-

up diagnostic routines; they are both zero during normal

operation.

25 Green LED Request; 0=Off, 1=On. The state of this bit

normally follows the "Downlink Detect" LED on the IFDR.

Loading...

Loading...