7 Series FPGAs GTP Transceivers User Guide www.xilinx.com 115

UG482 (v1.9) December 19, 2016

TX Configurable Driver

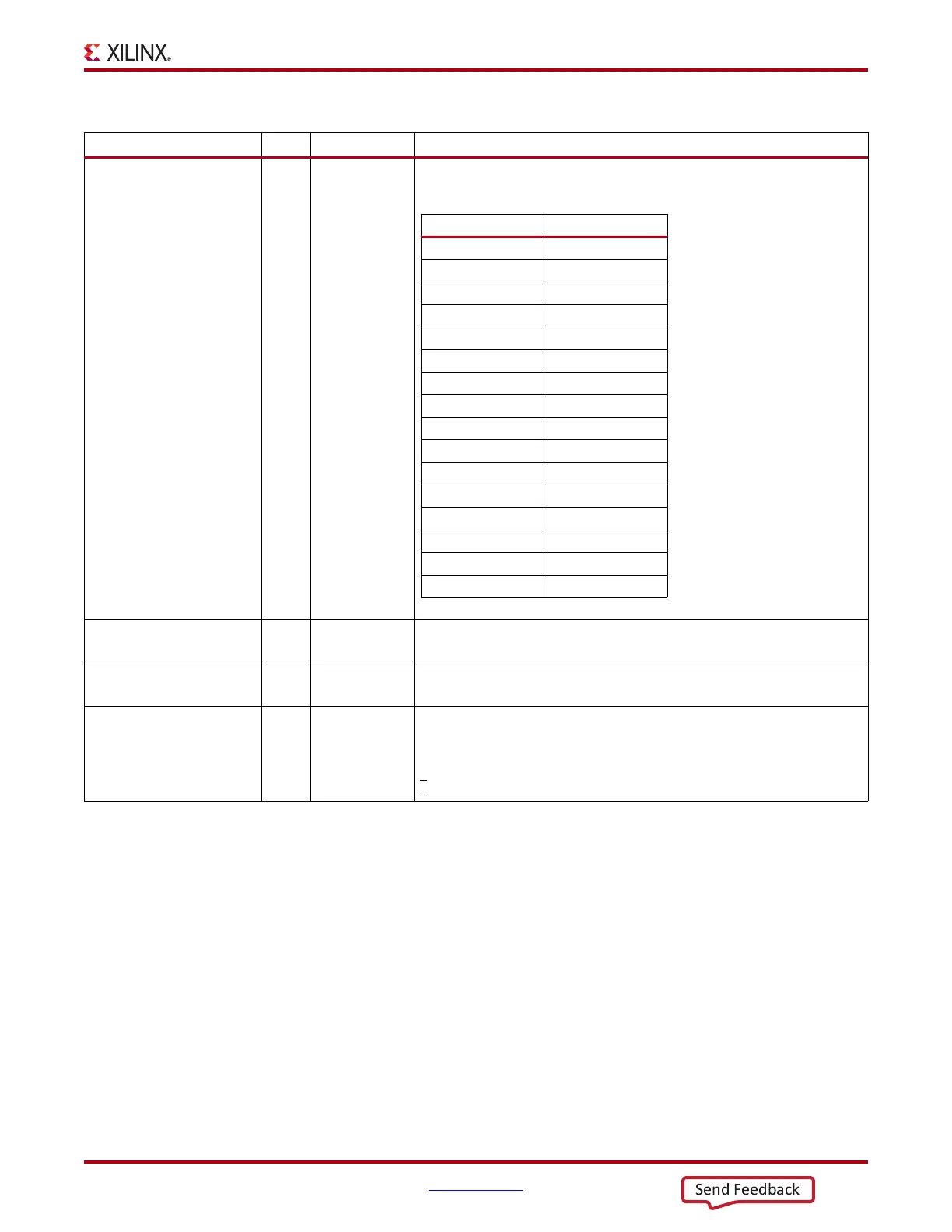

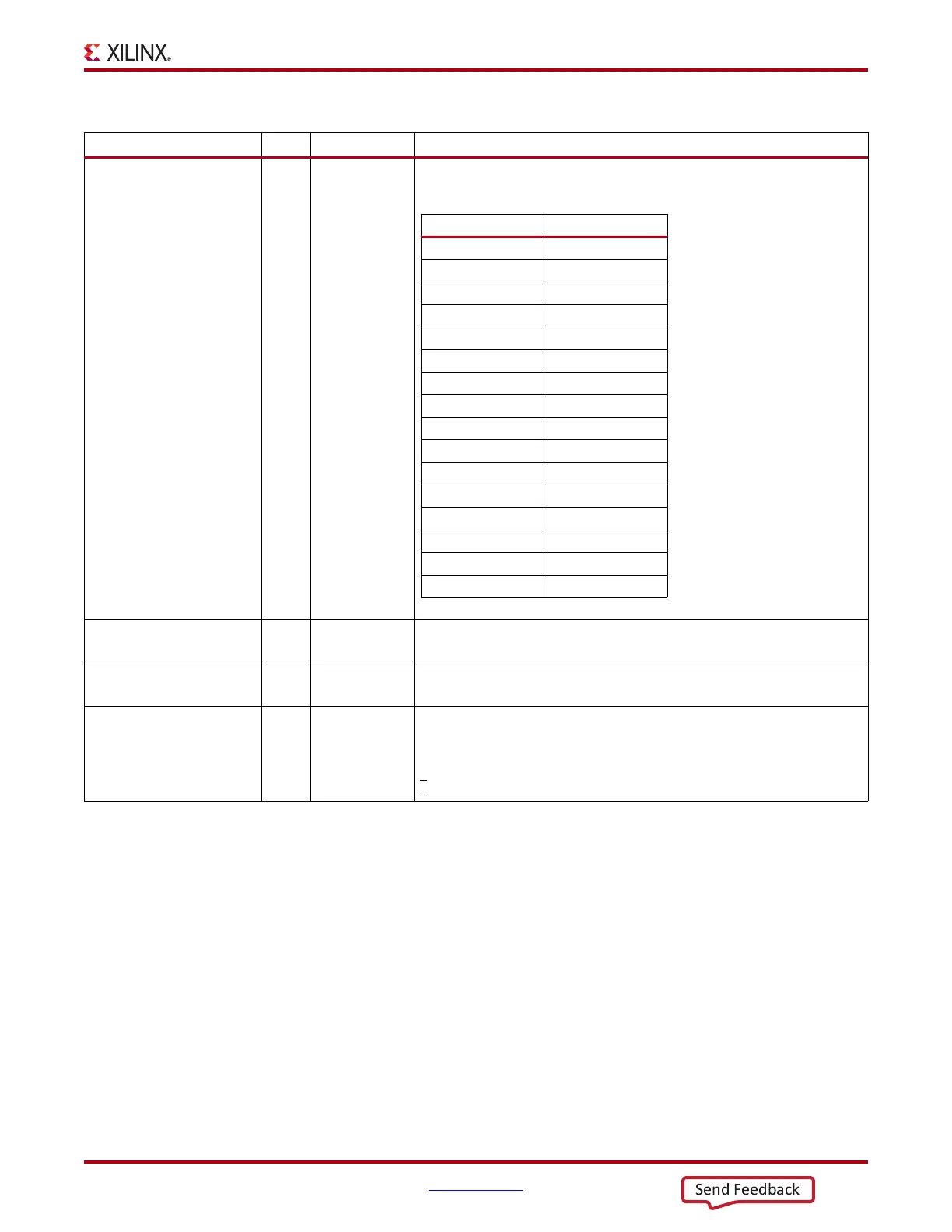

TXDIFFCTRL[3:0] In Async Driver Swing Control. The default is user specified. All listed values are in

mV

PPD

.

TXELECIDLE In TXUSRCLK2 When High, this signal forces GTPTXP and GTPTXN both to Common

mode, creating an electrical idle signal.

TXINHIBIT In TXUSRCLK2 When High, this signal blocks transmission of TXDATA and forces

GTPTXP to 0 and GTPTXN to 1.

TXMAINCURSOR[6:0] In Async Allows the main cursor coefficients to be directly set if the

TX_MAINCURSOR_SEL attribute is set to 1'b1.

51 – TXPOSTCURSOR coefficient units – TXPRECURSOR coefficient units

<

TXMAINCURSOR coefficient units

<

80 –TXPOSTCURSOR coefficient units – TXPRECURSOR coefficient units.

Table 3-28: TX Configurable Driver Ports (Cont’d)

Port Dir Clock Domain Description

[3:0] mV

PPD

4'b0000 253

4'b0001 316

4'b0010 377

4'b0011 439

4'b0100 499

4'b0101 561

4'b0110 621

4'b0111 682

4'b1000 743

4'b1001 799

4'b1010 857

4'b1011 909

4'b1100 959

4'b1101 1002

4'b1110 1043

4'b1111 1074

Loading...

Loading...