116 www.xilinx.com 7 Series FPGAs GTP Transceivers User Guide

UG482 (v1.9) December 19, 2016

Chapter 3: Transmitter

TXMARGIN[2:0] In Async TX Margin control for PCI Express PIPE 2.0 Interface. These signals are

mapped internally to TXDIFFCTRL/TXBUFDIFFCTRL via attributes.

PMARSVDIN1 In Async Reserved.

PMARSVDIN0 In Async Reserved.

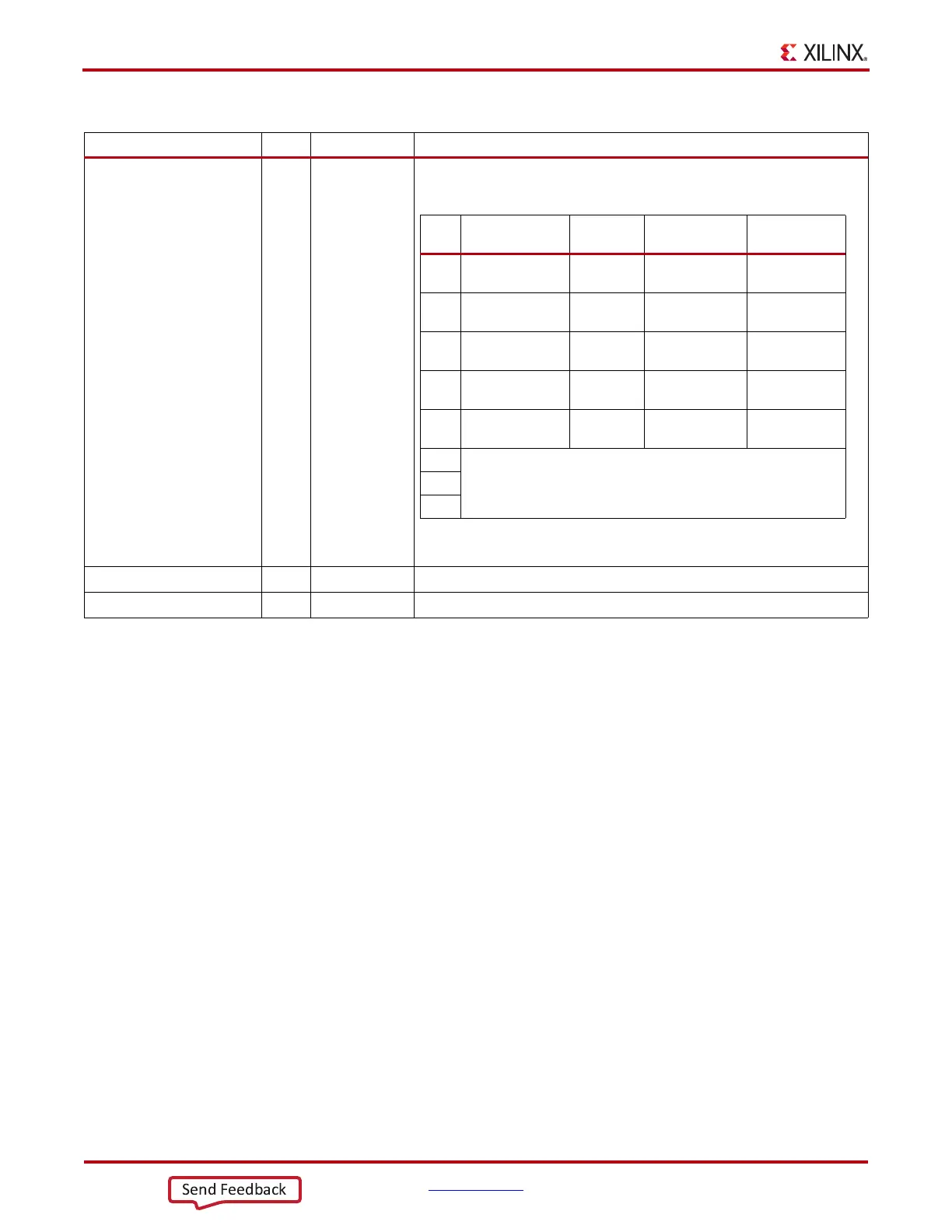

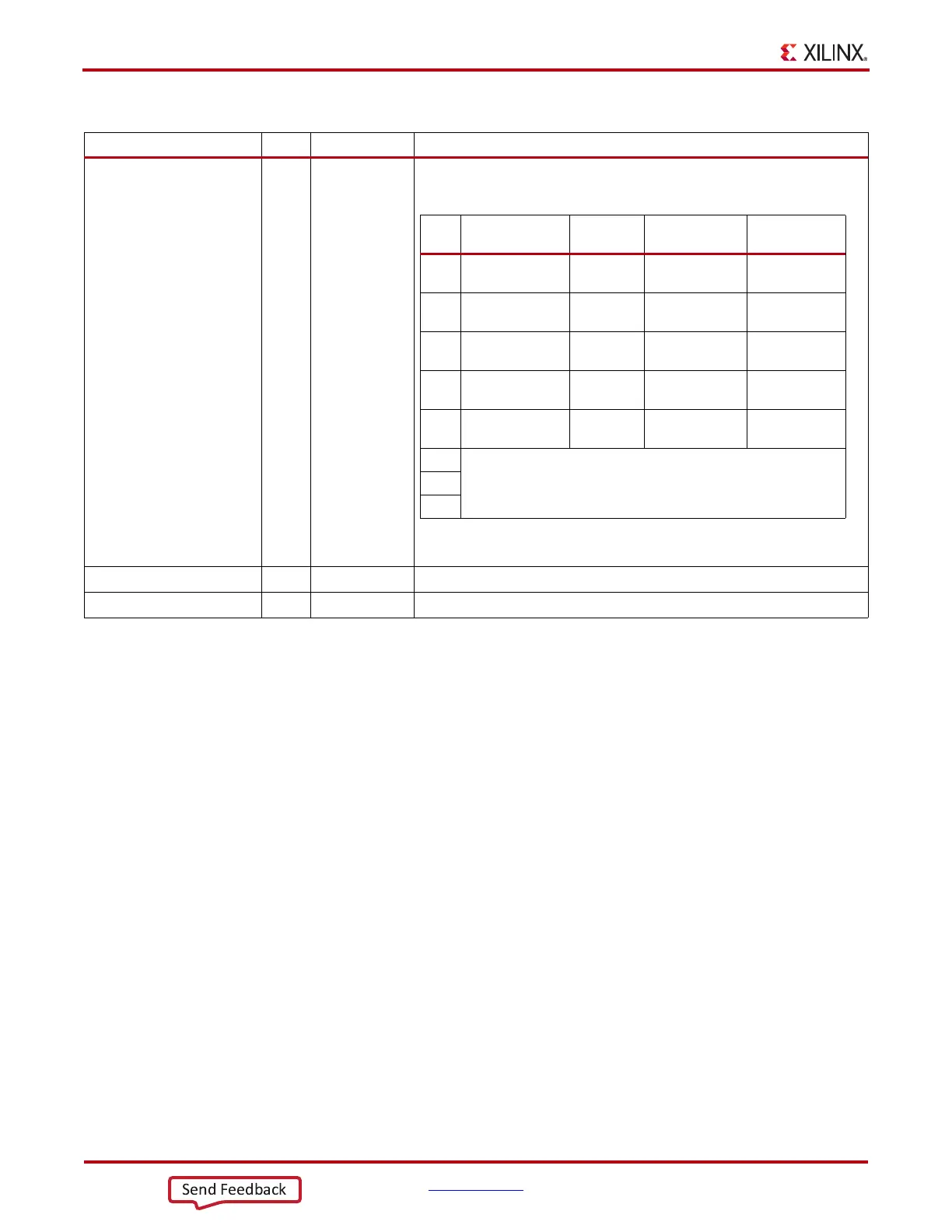

Table 3-28: TX Configurable Driver Ports (Cont’d)

Port Dir Clock Domain Description

[2:0] Full Range Half Range

Full Range

Attribute

Half Range

Attribute

000 800-1200 400-1200

TX_MARGIN_F

ULL_0

TX_MARGIN_

LOW_0

001 800-1200 400-700

TX_MARGIN_F

ULL_1

TX_MARGIN_

LOW_1

010 800-1200 400-700

TX_MARGIN_F

ULL_2

TX_MARGIN_

LOW_2

011 200-400 100-200

TX_MARGIN_F

ULL_3

TX_MARGIN_

LOW_3

100 100-200 100-200

TX_MARGIN_F

ULL_4

TX_MARGIN_

LOW_4

101

default to “DIRECT” mode110

111

Loading...

Loading...