198 www.xilinx.com 7 Series FPGAs GTP Transceivers User Guide

UG482 (v1.9) December 19, 2016

Chapter 4: Receiver

skew between each lane and adjust the latency of RX elastic buffers, so that data is presented

without skew at the RX fabric user interface.

RX channel bonding supports 8B/10B encoded data but does not support these encoded data types:

• 64B/66B

• 64B/67B

• 128B/130B

• Scrambled data

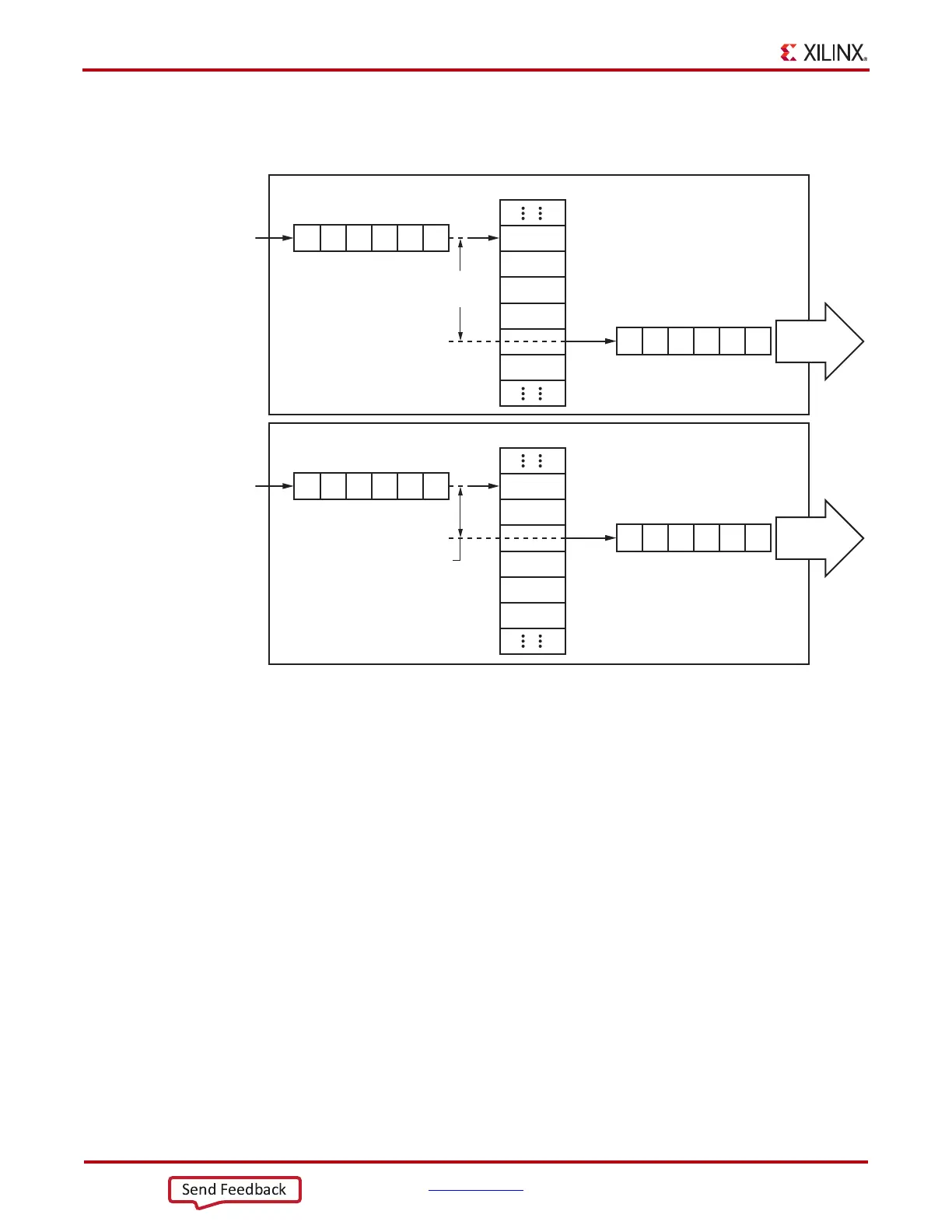

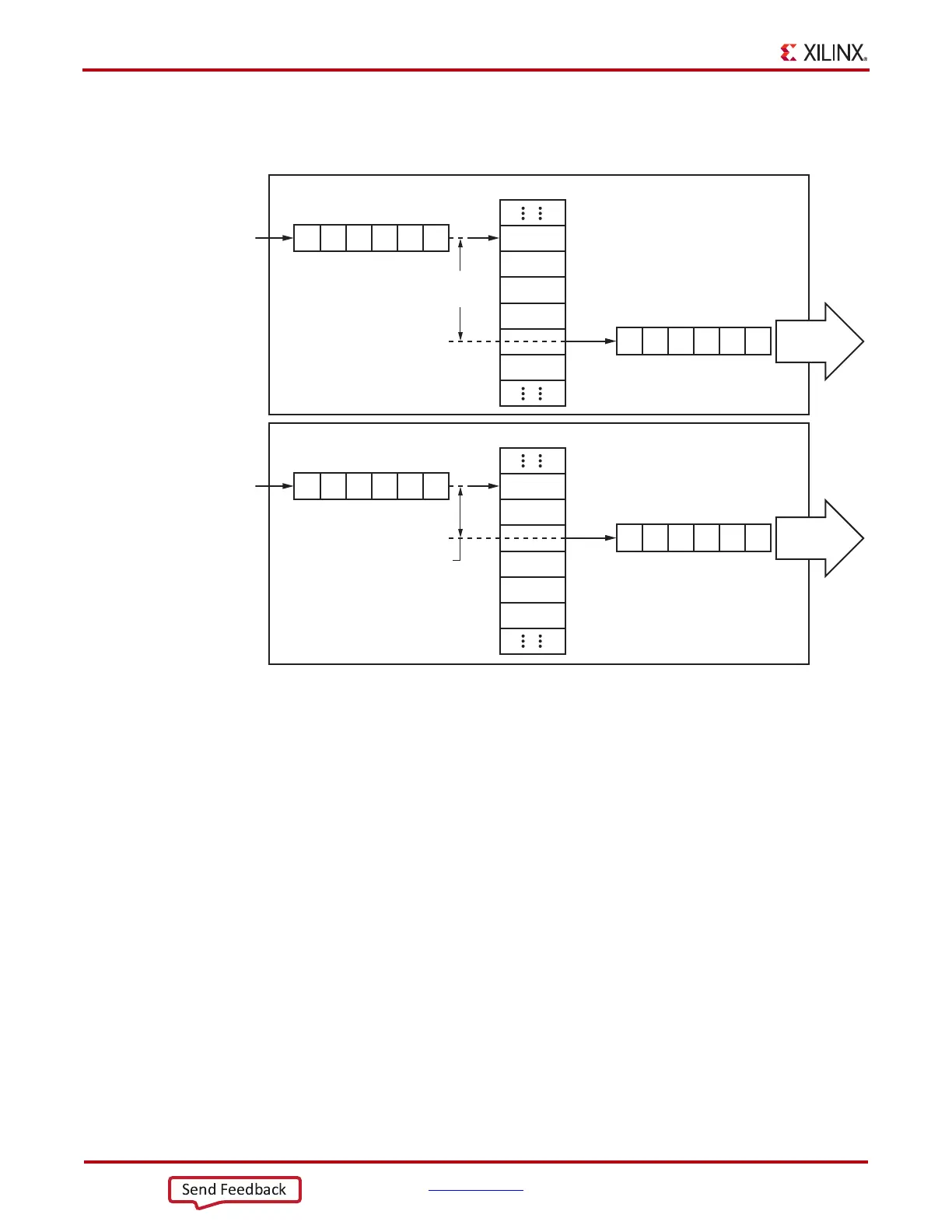

X-Ref Target - Figure 4-47

Figure 4-47: Channel Bonding Conceptual View

Elastic Buffer

GTP0 (Master)

GTP1 (Slave)

UG482_c4_29_111011

Deskewed

Data

RX Data in Two Clock Cycles

Ahead of GTP1 Data

Set to 4 Cycles of Latency by

Channel Bonding Controller

data data

SEQ

4

SEQ

3

SEQ

2

SEQ

1

Elastic Buffer

RX Data in Two Clock Cycles

Behind GTP0 Data

Set to 2 Cycles of Latency by

Channel Bonding Controller

data data

SEQ

4

SEQ

3

SEQ

2

SEQ

1

data data

SEQ

4

SEQ

3

SEQ

2

SEQ

1

Deskewed

Data

data data

SEQ

4

SEQ

3

SEQ

2

SEQ

1

Loading...

Loading...