272 www.xilinx.com 7 Series FPGAs GTP Transceivers User Guide

UG482 (v1.9) December 19, 2016

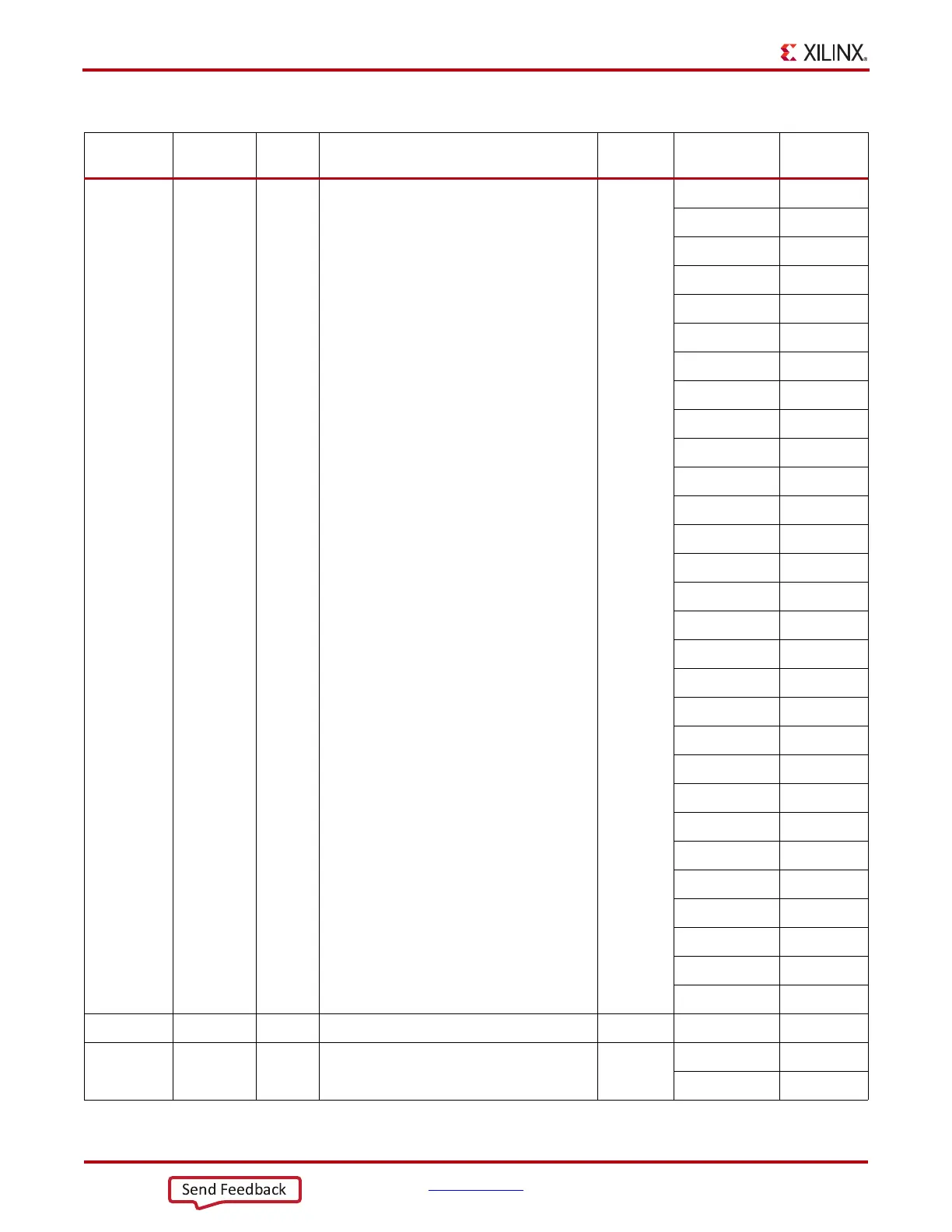

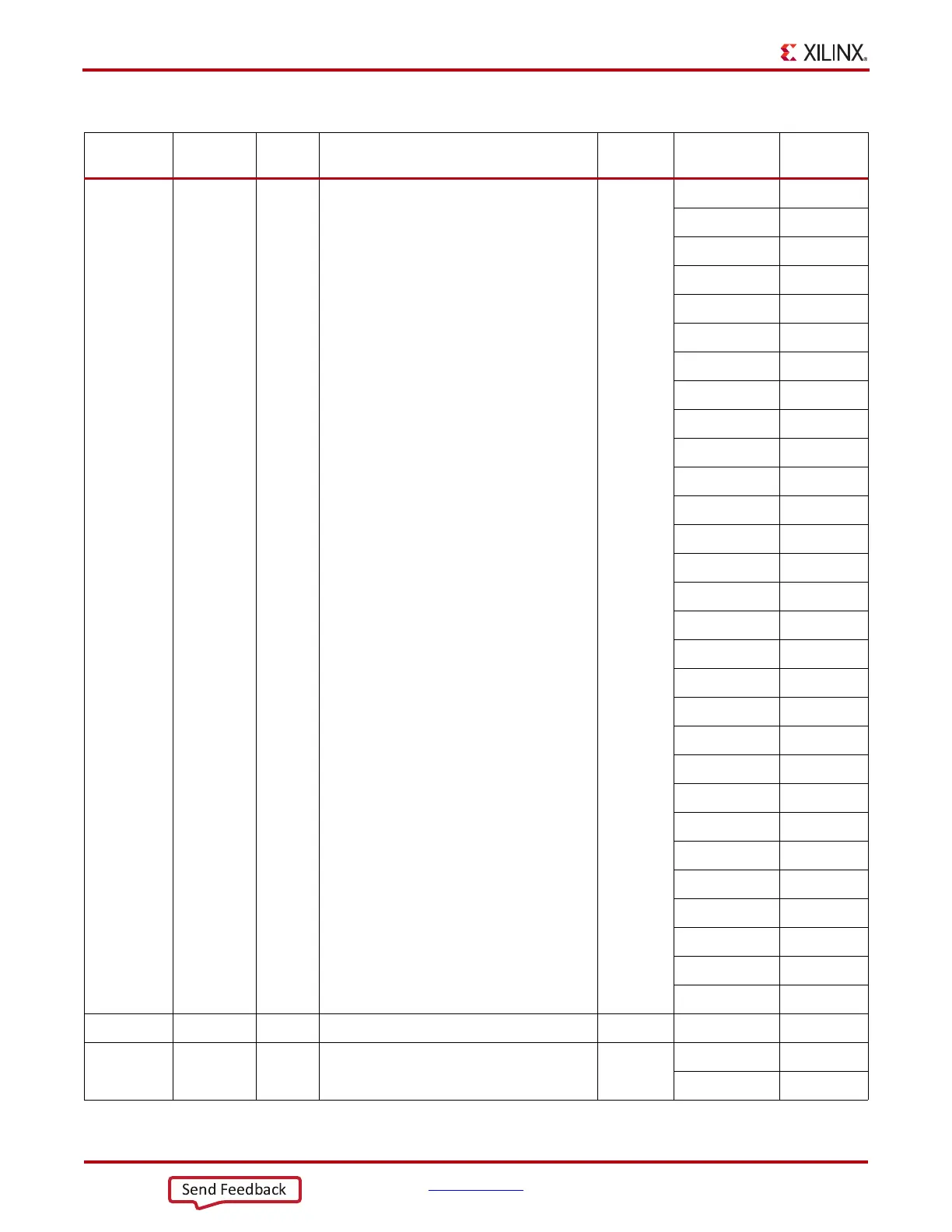

Appendix D: DRP Address Map of the GTP Transceiver

0013

(Cont’d)

8:3 R/W SATA_MIN_BURST 5:0

33 33

34 34

35 35

36 36

37 37

38 38

39 39

40 40

41 41

42 42

43 43

44 44

45 45

46 46

47 47

48 48

49 49

50 50

51 51

52 52

53 53

54 54

55 55

56 56

57 57

58 58

59 59

60 60

61 61

0013 2:0 R/W SATA_EIDLE_VAL 2:0 0-7 0-7

0014 11:6 R/W SATA_MIN_WAKE 5:0

11

22

Table D-2: DRP Map of GTPE2_CHANNEL Primitive (Cont’d)

DRP

Address

DRP Bits R/W Attribute Name

Attribute

Bits

Attribute

Encoding

DRP

Encoding

Loading...

Loading...