46 www.xilinx.com 7 Series FPGAs GTP Transceivers User Guide

UG482 (v1.9) December 19, 2016

Chapter 2: Shared Features

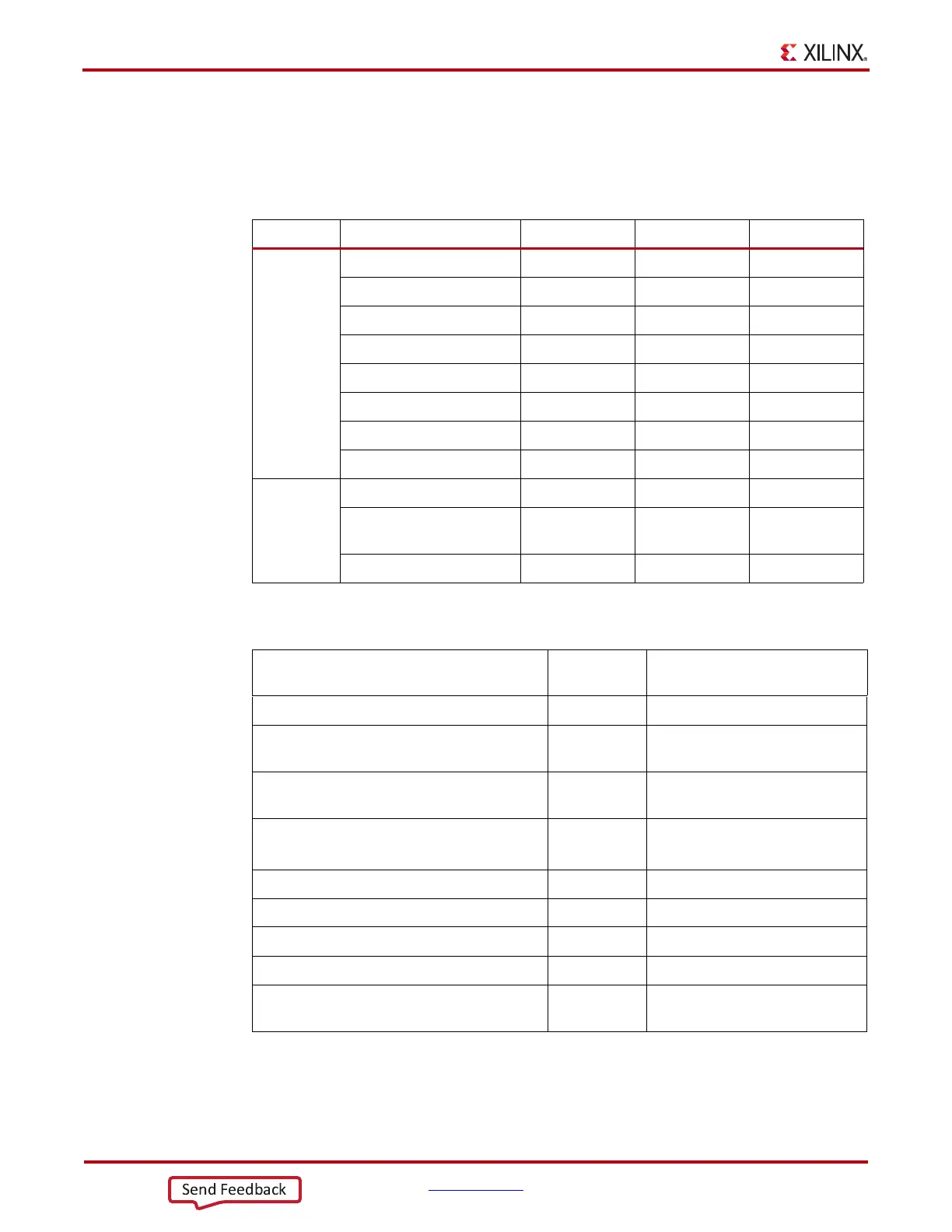

Table 2-16 summarizes all resets available to the GTP transceiver TX and components affected by

them in sequential mode. Using TXPMARESET in sequential mode resets everything covered by

GTTXRESET except the TX reset state machine.

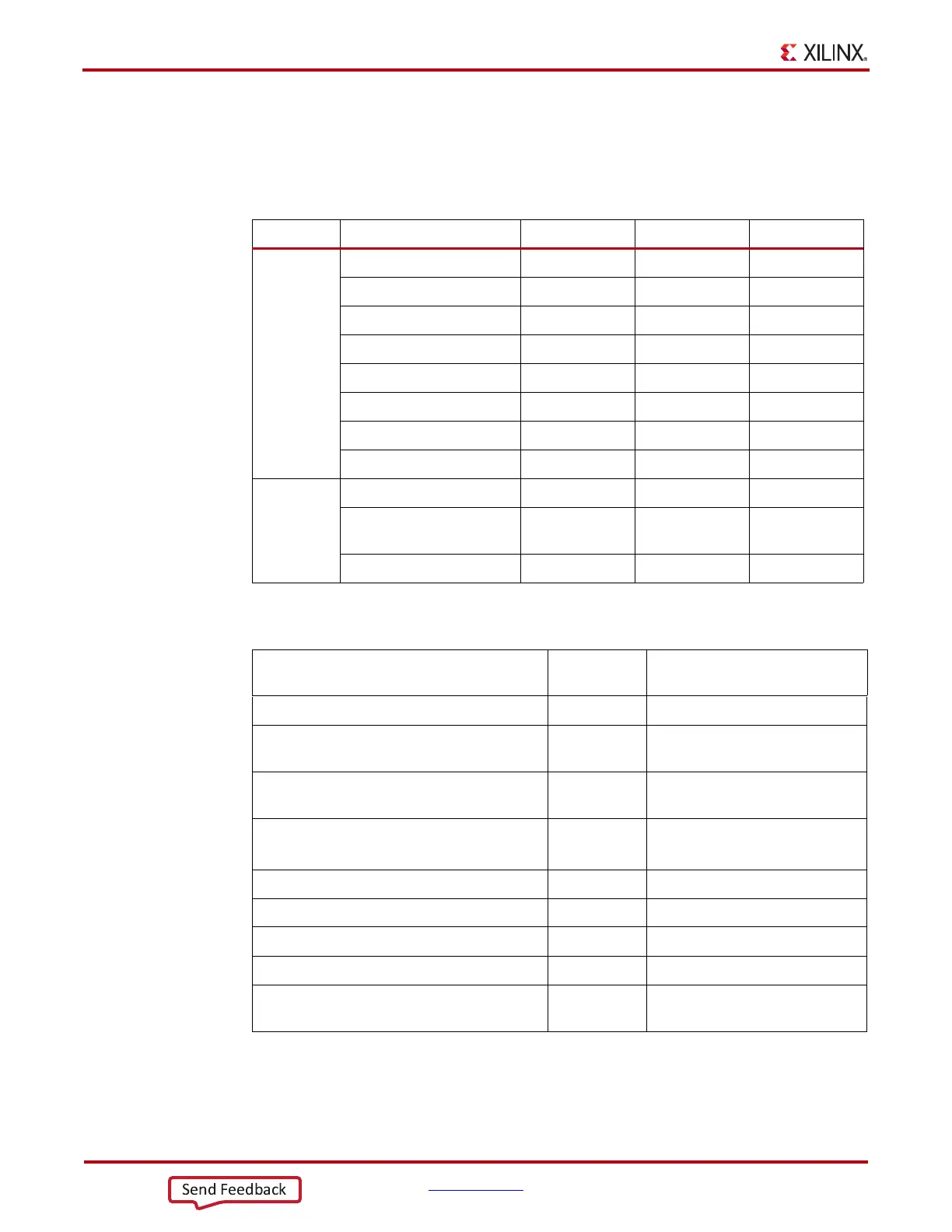

Table 2-17 lists the recommended resets for various situations.

Table 2-16: TX Initialization Reset and Component Reset Coverage

in Sequential Mode

Functional Blocks GTTXRESET TXPMARESET TXPCSRESET

TX PCS

FPGA TX Fabric Interface √√√

TX 8B/10B Encoder √√√

TX Gearbox √√√

TX Buffer √√√

TX Pattern Generator √√√

TX Polarity Control √√√

TX Out-of-Band Signaling √√√

TX Reset FSM √

TX PMA

TX Configuration Driver √√

TX Receiver Detect for PCI

Express Designs

√√

TX PISO √√

Table 2-17: Recommended Resets for Common Situations

Situation

Components

to be Reset

Recommended Reset

(1)

After power up and configuration Entire TX GTTXRESET

After turning on a reference clock to the PLL

being used

Entire TX GTTXRESET

After changing the reference clock to the PLL

being used

Entire TX GTTXRESET

After assertion/deassertion of

PLL[0/1]PD, for the PLL being used

Entire TX GTTXRESET

After assertion/deassertion of TXPD[1:0] Entire TX GTTXRESET

TX rate change TX PCS Reset performed automatically

TX parallel clock source reset TX PCS TXPCSRESET

After entering or exiting far-end PMA loopback Entire TX GTTXRESET

After entering or exiting near-end PMA

loopback

Entire RX GTRXRESET

1. The recommended reset has the smallest impact on the other components of the GTP transceiver.

Loading...

Loading...