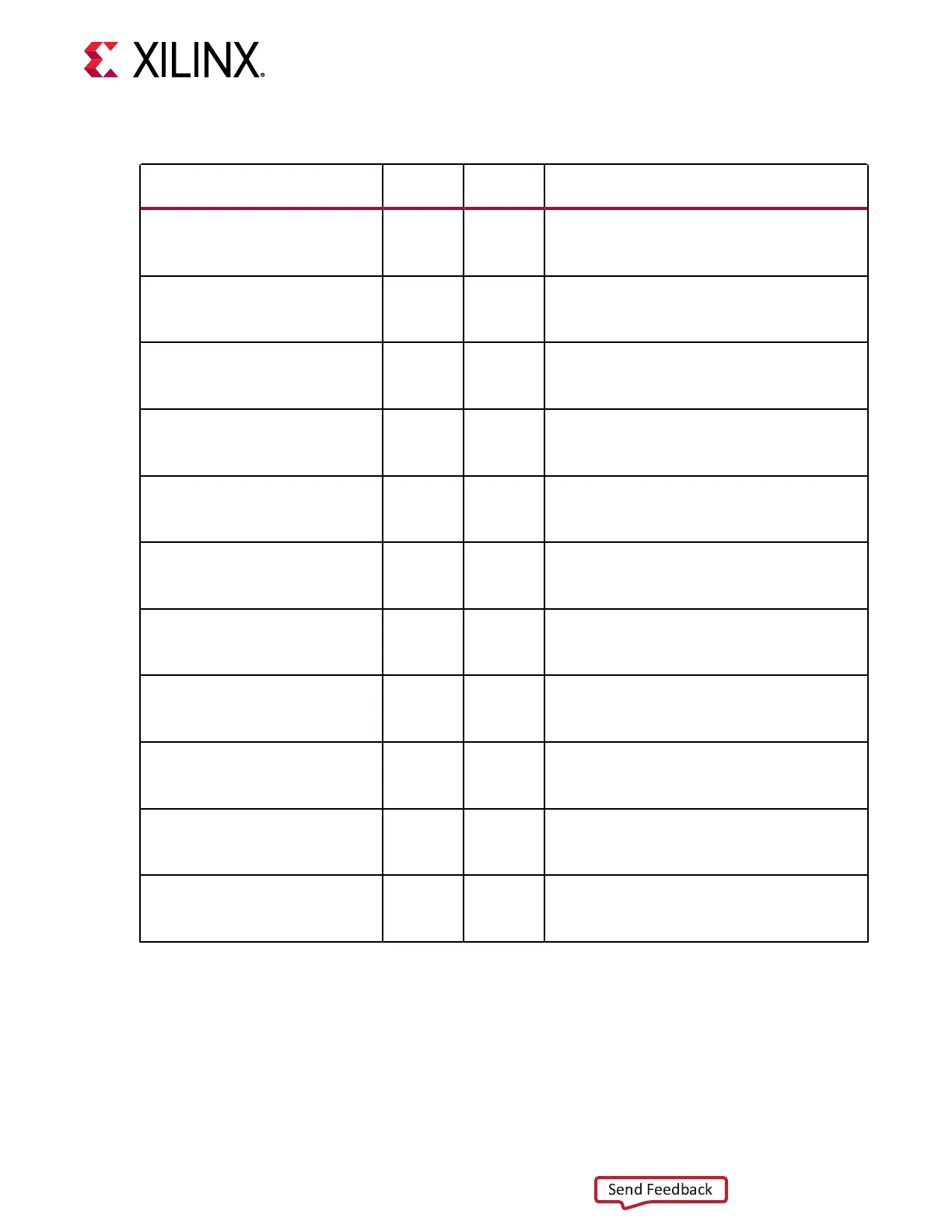

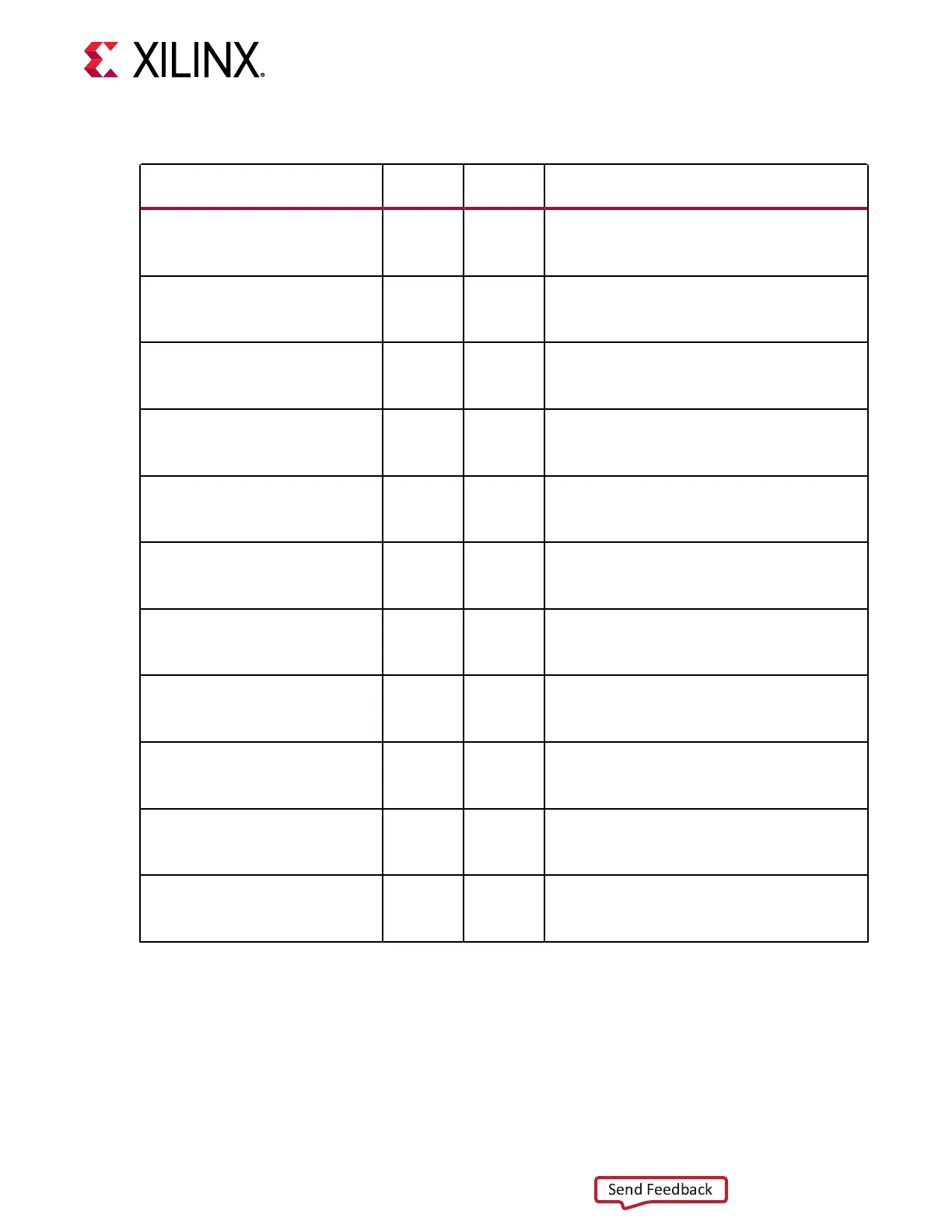

Table 17: RX Initialization and Reset Ports (cont'd)

Port Dir

Clock

Domain

Description

CH[0/1]_RXADCCLKGENRESET In Async This port is driven High and then deasserted to start

a single mode reset on RX ADC CLKGEN. The reset is

not dependent on RXRESETMODE or

RXPMARESETMASK setting.

CH[0/1]_RXBUFRESET In Async This port is driven High and then deasserted to start

a single mode reset on RX buffer. The reset is not

dependent on RXRESETMODE or RXPCSRESETMASK

setting.

CH[0/1]_RXCDRFRRESET In Async This port is driven High and then deasserted to start

a single mode reset on CDR FR. The reset is not

dependent on RXRESETMODE or RXPMARESETMASK

setting.

CH[0/1]_RXCDRPHRESET In Async This port is driven High and then deasserted to start

a single mode reset on CDR PH. The reset is not

dependent on RXRESETMODE or RXPMARESETMASK

setting.

CH[0/1]_RXDFERESET In Async This port is driven High and then deasserted to start

a single mode reset on DFE. The reset is not

dependent on RXRESETMODE or RXPMARESETMASK

setting.

CH[0/1]_RXDSPRESET In Async This port is driven High and then deasserted to start

a single mode reset on DSP. The reset is not

dependent on RXRESETMODE or RXPMARESETMASK

setting.

CH[0/1]_RXEYESCANRESET In Async This port is driven High and then deasserted to start

a single mode reset on eye scan. The reset is not

dependent on RXRESETMODE or RXPCSRESETMASK

setting.

CH[0/1]_RXFECRESET In Async This port is driven High and then deasserted to start

a single mode reset on the FEC. The reset is not

dependent on RXRESETMODE or RXPCSRESETMASK

setting.

CH[0/1]_RXPCSRESET In Async This port is driven High and then deasserted to start

a single mode reset on the PCS top. The reset is not

dependent on RXRESETMODE or RXPCSRESETMASK

setting.

CH[0/1]_RXPMARESET In Async This port is driven High and then deasserted to start

a single mode reset on the PMA top. The reset is not

dependent on RXRESETMODE or RXPMARESETMASK

setting.

CH[0/1]_RXPRBSCNTRESET In Async This port is driven High and then deasserted to start

a single mode reset on the PRBS counter. The reset is

not dependent on RXRESETMODE or

RXPCSRESETMASK setting.

Chapter 2: Shared Features

UG581 (v1.0) January 4, 2019 www.xilinx.com

Virtex UltraScale+ GTM Transceivers 37

Loading...

Loading...