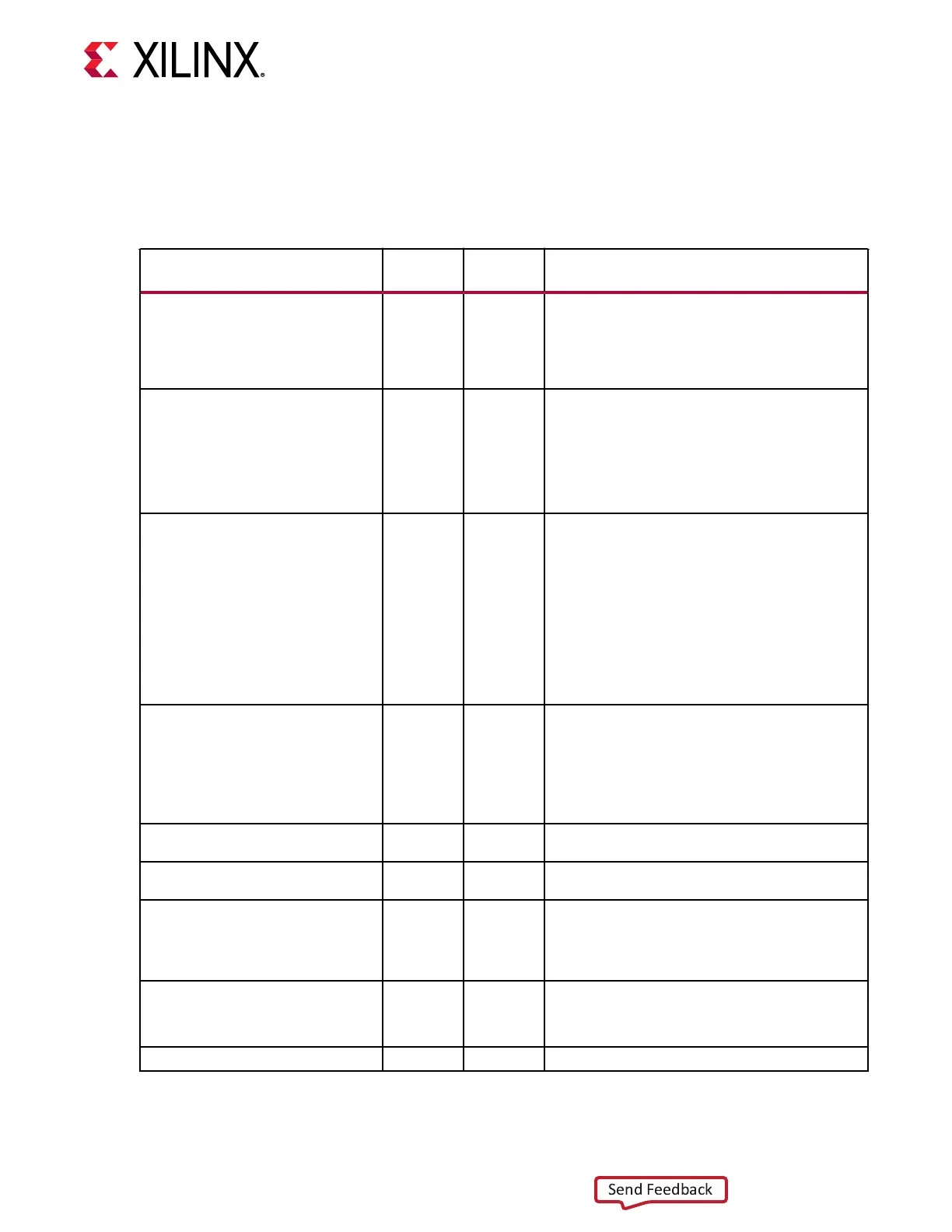

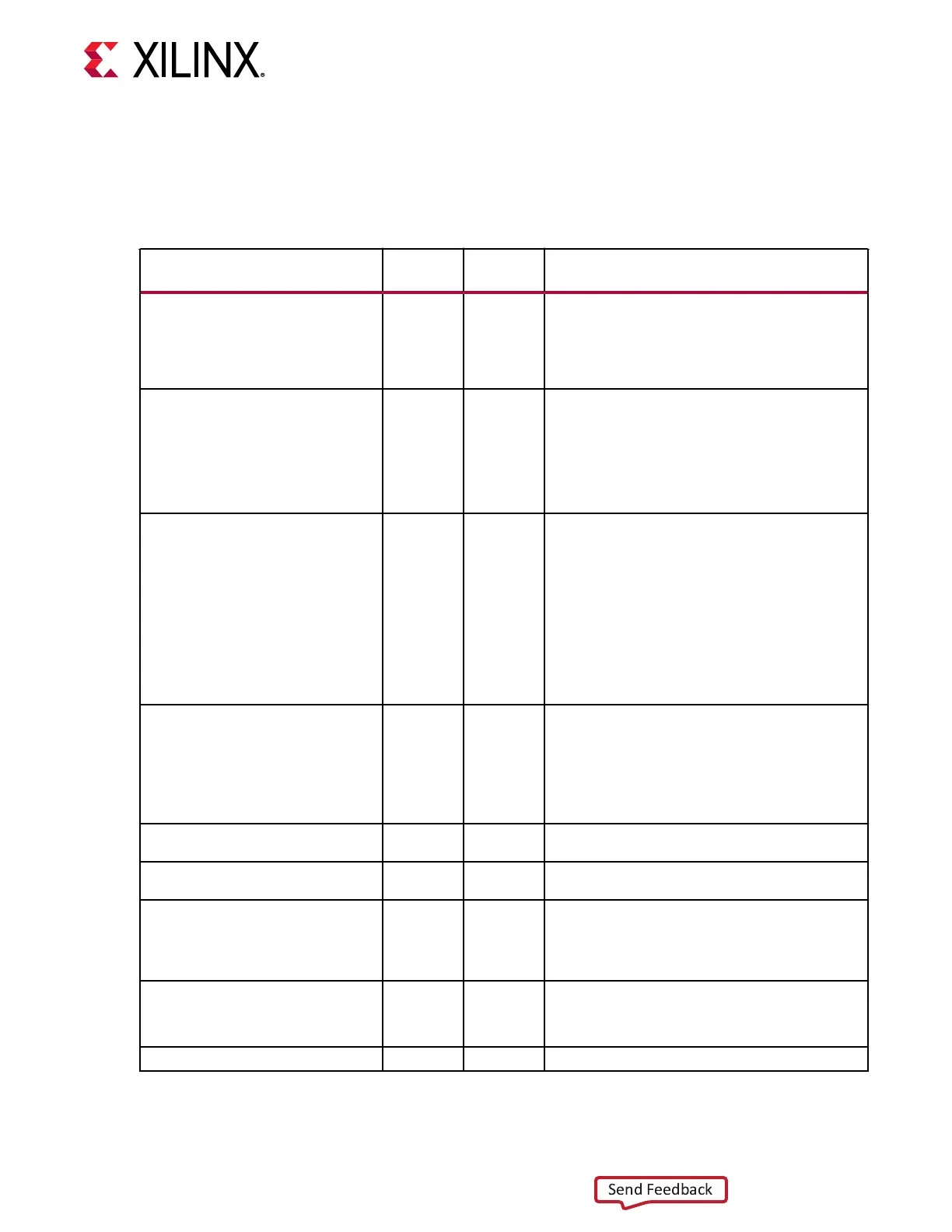

Ports and Attributes

The following table lists the ports required by the GTM transceiver RX inializaon process.

Table 17: RX Initialization and Reset Ports

Port Dir

Clock

Domain

Description

CH[0/1]_GTRXRESET In Async This port is driven High and then deasserted to start

a RX reset sequence. The components to be reset are

determined by RXPMARESETMASK and

RXPCSRESETMASK. In sequential mode, the resets are

performed sequentially. In single mode, the resets

are performed simultaneously.

CH[0/1]_RXRESETMODE[1:0]

In Async Reset mode port for RX:

2’b00: Sequential mode (recommended).

2’b01: Reserved.

2’b10: Reserved.

2’b11: Single mode.

CH[0/1]_RXPMARESETMASK[7:0]

In Async RX PMA reset mask selection:

Bit 7: Reserved.

Bit 6: CDR FR.

Bit 5: CDR PH.

Bit 4: Adapt.

Bit 3: DFE.

Bit 2: DSP.

Bit 1: ADC CLKGEN.

Bit 0: RX PMA Top.

CH[0/1]_RXPCSRESETMASK[3:0]

In Async RX PCS reset mask selection

Bit 3: PRBS counter.

Bit 2: RX PCS top.

Bit 1: FEC.

Bit 0: Eye Scan.

CH[0/1]_RXUSERRDY

In Async This port is driven High by the user application when

RXUSRCLK is stable.

CH[0/1]_RXPMARESETDONE Out Async This active-High signal indicates RX PMA reset is

complete.

CH[0/1]_RXRESETDONE Out RXUSRCLK This active-High signal indicates the GTM transceiver

RX has finished reset and is ready for use. This port is

driven Low when GTRXRESET goes High and is not

driven High until the GTM transceiver has completed

all RX reset steps.

CH[0/1]_RXADAPTRESET

In Async This port is driven High and then deasserted to start

a single mode reset on RX adaptation. The reset is

not dependent on RXRESETMODE or

RXPMARESETMASK setting.

CH[0/1]_RXADCCALRESET In Async Reserved.

Chapter 2: Shared Features

UG581 (v1.0) January 4, 2019 www.xilinx.com

Virtex UltraScale+ GTM Transceivers 36

Loading...

Loading...