The following table lists aributes required by GTM transceiver RX inializaon. In general cases,

the reset me required by the RX PMA or the RX PCS varies depending on line rate. The factors

aecng PMA reset me and PCS reset me are the user-congurable aributes

RX_PMA_RESET_TIME, RX_DFE_RESET_TIME, RX_ADAPT_RESET_TIME,

RX_DSP_RESET_TIME, RX_ADC_CLKGEN_RESET_TIME, RX_CDRFREQ_RESET_TIME,

RX_CDRPHASE_RESET_TIME, RX_PCS_RESET_TIME, RX_FEC_RESET_TIME,

RX_PRBS_RESET_TIME and RX_EYESCAN_RESET_TIME.

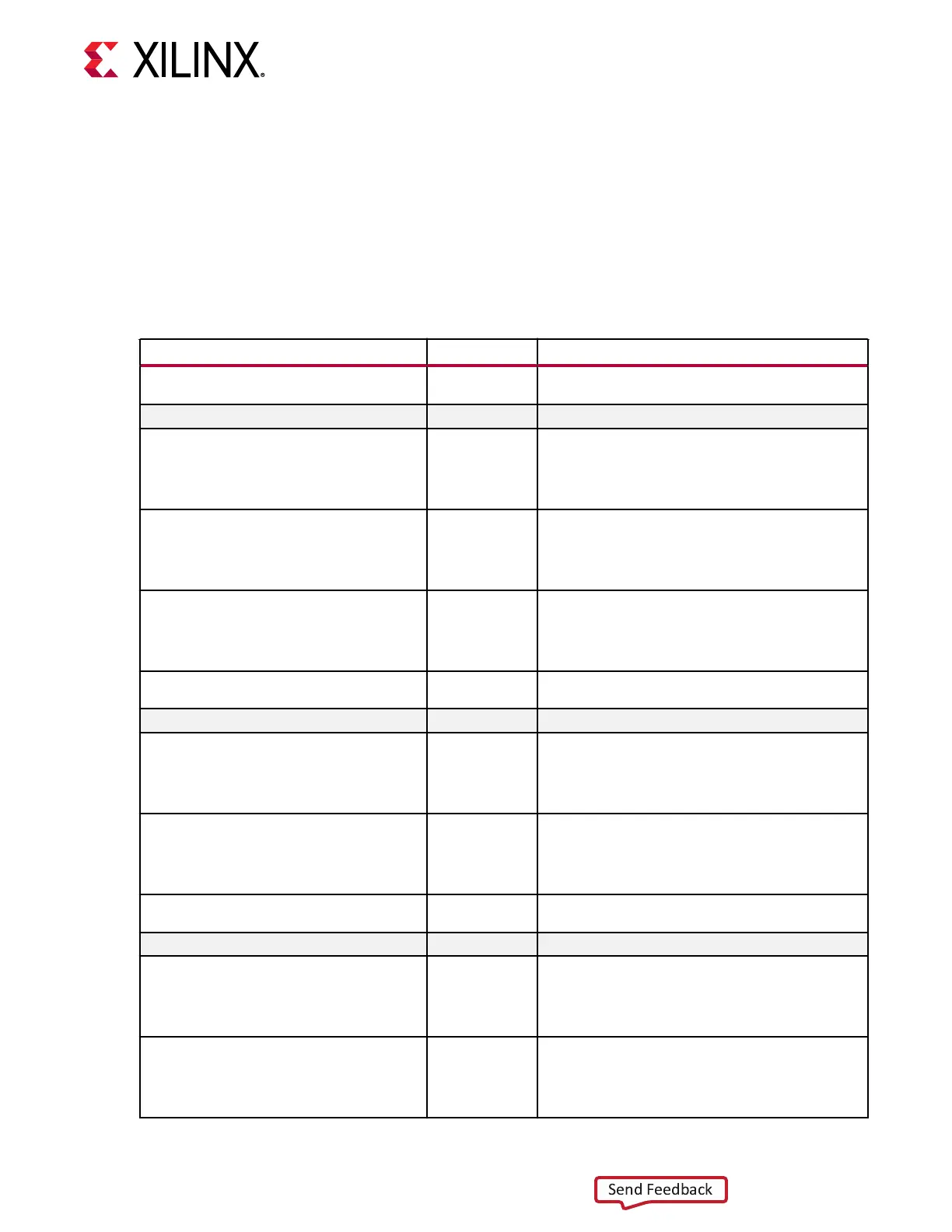

Table 18: RX Initialization and Reset Attributes

Attribute Type Description

CH[0/1]_RST_TIME_CFG2 16-bit Reserved. Use the recommended value from the

Wizard.

Bit Name Bit Field Description

RX_ADAPT_RESET_TIME [14:10] Reserved. Represents the time duration to apply an RX

adapt reset. Use the recommended value from the

Wizard. Must be a non-zero value when

RXPMARESETMASK[4] is High and GTRXRESET initiates

the reset process.

RX_DSP_RESET_TIME

[9:5] Reserved. Represents the time duration to apply an RX

DSP reset. Use the recommended value from the

Wizard. Must be a non-zero value when

RXPMARESETMASK[2] is High and GTRXRESET initiates

the reset process.

RX_ADC_CLKGEN_RESET_TIME

[4:0] Reserved. Represents the time duration to apply an RX

ADC CLKGEN reset. Use the recommended value from

the Wizard. Must be a non-zero value when

RXPMARESETMASK[1] is High and GTRXRESET initiates

the reset process.

CH[0/1]_RST_TIME_CFG3

16-bit Reserved. Use the recommended value from the

Wizard.

Bit Name Bit Field Description

RX_CDRFREQ_RESET_TIME [14:10] Reserved. Represents the time duration to apply an RX

CDR FR reset. Use the recommended value from the

Wizard. Must be a non-zero value when

RXPMARESETMASK[5] is High and GTRXRESET initiates

the reset process.

RX_CDRPHASE_RESET_TIME

[9:5] Reserved. Represents the time duration to apply an RX

CDR PH reset. Use the recommended value from the

Wizard. Must be a non-zero value when

RXPMARESETMASK[6] is High and GTRXRESET initiates

the reset process.

CH[0/1]_RST_TIME_CFG1

16-bit Reserved. Use the recommended value from the

Wizard.

Bit Name Bit Field Description

RX_DFE_RESET_TIME [14:10] Reserved. Represents the time duration to apply an RX

DFE reset. Use the recommended value from the

Wizard. Must be a non-zero value when

RXPMARESETMASK[3] is High and GTRXRESET initiates

the reset process.

RX_PMA_RESET_TIME

[9:5] Reserved. Represents the time duration to apply an RX

PMA reset. Use the recommended value from the

Wizard. Must be a non-zero value when

RXPMARESETMASK[0] is High and GTRXRESET initiates

the reset process.

Chapter 2: Shared Features

UG581 (v1.0) January 4, 2019 www.xilinx.com

Virtex UltraScale+ GTM Transceivers 38

Loading...

Loading...