MC81F4204

April 24, 2012 Ver.1.41 129

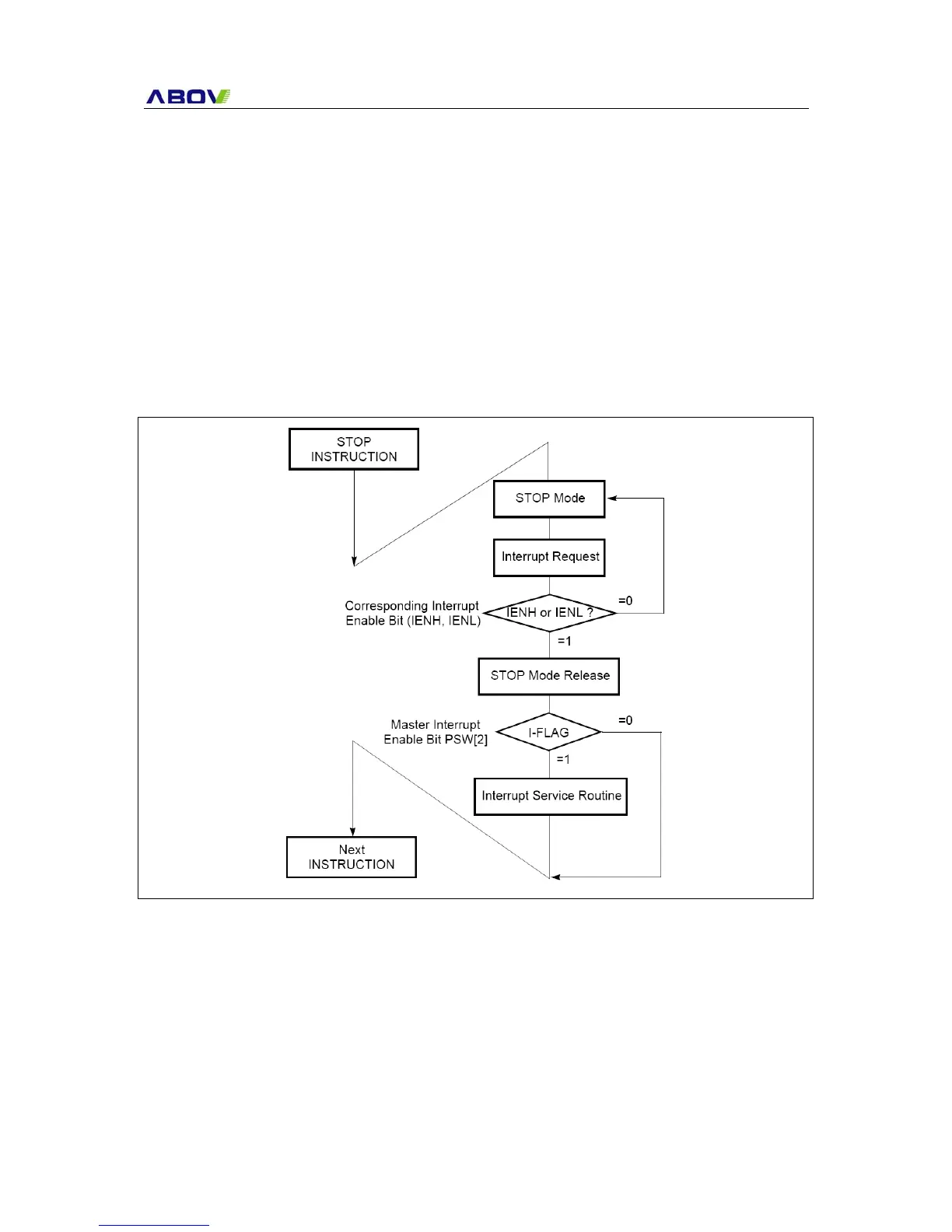

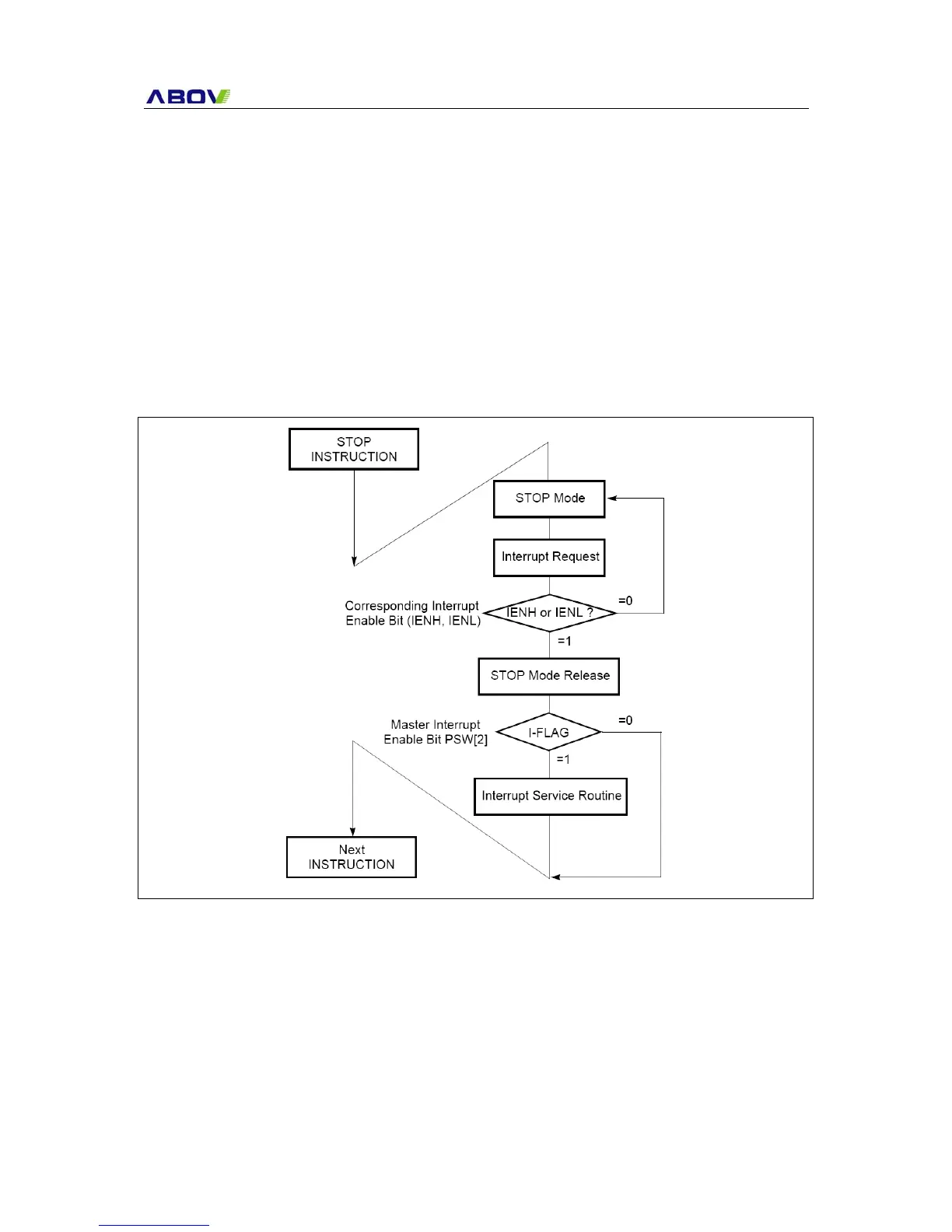

Release the STOP mode

The source for exit from STOP mode is hardware reset, external interrupt, Timer(EC0,1,2), SIO.

Reset re-defines all the Control registers but does not change the on-chip RAM.

If I-flag = 1, the normal interrupt response takes place. If I-flag = 0, the chip will resume execution

starting with the instruction following the STOP instruction. It will not vector to interrupt service routine.

(refer to

Figure 23-3) When exit from Stop mode by external interrupt, enough oscillation stabilization

time is required to normal operation.

Figure 23-4 shows the timing diagram. When released from the

Stop mode, the Basic interval timer is activated on wake-up. It is increased from 00

H until FFH. The

count overflow is set to start normal operation. Therefore, before STOP instruction, user must be set

its relevant prescaler divide ratio to have long enough time (more than 20msec). This guarantees that

oscillator has started and stabilized. By reset, exit from Stop mode is shown in

Figure 23-5.

Figure 23-3 STOP Releasing Flow by Interrupts

Loading...

Loading...