MC81F4204

96 April 24, 2012 Ver.1.41

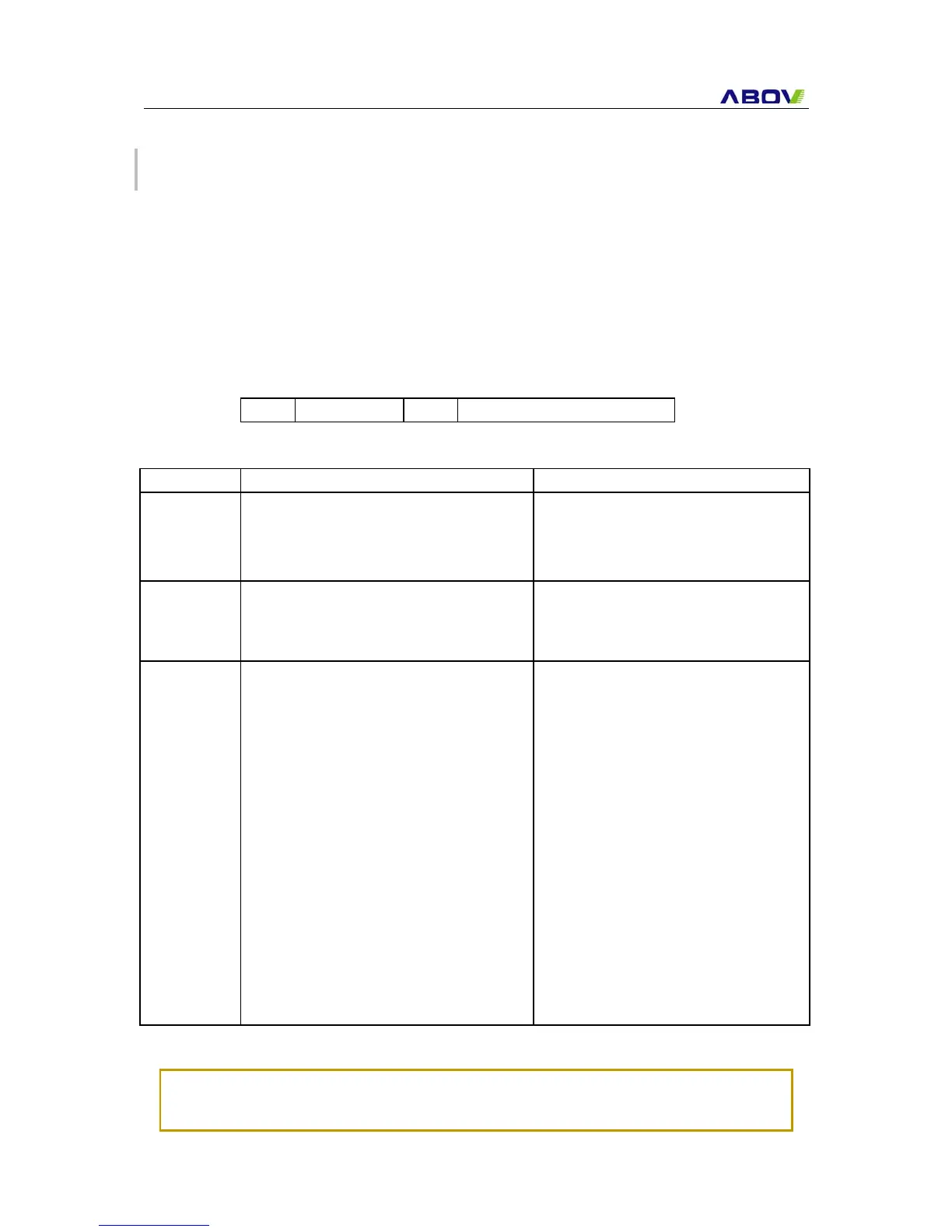

T0SCR

TIMER 0 STATUS AND CONROL REGISTER 00B0H

To enable the timer 0 match interrupt, you must set “1” to T0MIE(IENH.7).

When the timer 0 match interrupt sub-routine is serviced, the timer 0 match interrupt request flag bit,

T0MIR(IRQH.7), is automatically cleared.

To enable the timer 0 overflow interrupt, you must set “1” to T0OVIE(IENH.6).

When the timer 0 overflow interrupt sub-routine is serviced, the timer 0 overflow interrupt request flag

bit, T0OVIF(IRQH.6), is automatically cleared.

7 6 5 4 3 2 1 0

T0SCR

T0MOD T0MS T0CC T0CS

Reset value: 00H

R/W R/W R/W R/W R/W R/W R/W R/W

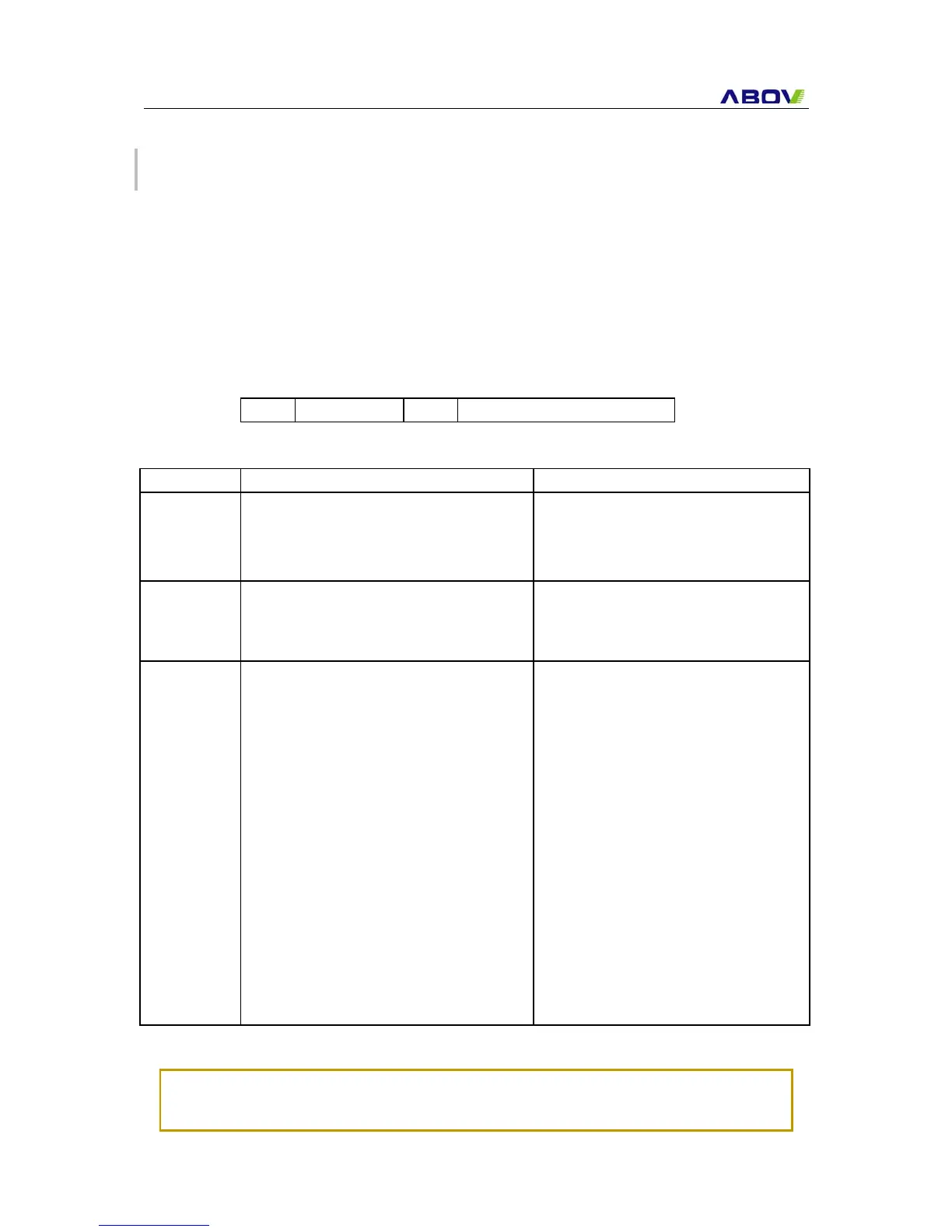

-

- Not used for MC81F4204

00: Interval mode (T0O)

01: PWM mode (OVF and match

interrupt can occur)

T0MS

Timer 0 Mode Selection Bit

1X: Capture mode (OVF can occur)

0: No effect

T0CC

Timer 0 Counter Clear Bit

1: Clear the Timer 0 counter (When

write, automatically cleared “0” after

being cleared counter)

0000: Counter stop

0001: Not available

0010: Not available

0011: Not available

0100: Not available

0101: External clock (EC0) rising edge

0110: External clock (EC0) falling edge

0111: Not available

1000: fxx/2

1001: fxx/4

1010: fxx/8

1011: fxx/16

1100: fxx/32

1101: fxx/128

1110: fxx/512

T0CS

Timer 0 Clock Selection Bits

1111: fxx/2048

Note :

You must set the T0CC(T0SCR.4) bit after set T0DR register. The timer 0 counter value is

compared with timer 0 buffer register instead of T0DR. And T0DR value is copied to timer 0

buffer register when 1)T0CC is set 2)T0OVIR is set 3) T0MIR is set.

Loading...

Loading...