High Power Electronic Load 63200A Series Operation & Programming Manual

Channel Summary 5.2.2

■ The Channel Summary registers summarize the channel status conditions up to 10

channels.

■ When an enabled bit in the Channel Status Event register is set, it causes the

corresponding channel bit in the Channel Summary Event register to be set.

■ Reading the Event register will reset it to zero.

■ The Channel Summary Enable register can be programmed to specify the channel

summary event bit from the existing channels that is logically ORed to become Bit 2

(CSUM bit) in the Status Byte register.

Questionable Status 5.2.3

■ The Questionable Status registers inform you one or more questionable status

conditions which indicate certain errors or faults have occurred to at least one channel.

Table 5-2 lists the questionable status conditions that are applied to the electronic load.

These conditions are same as the channel status conditions. Refer to Table 5-1 for a

complete description.

■ When a corresponding bit of Questionable Status Condition register is set, it indicates

the condition is true.

■ Program the PTR/NTR filter to select the way of condition transition in the Questionable

Status Condition register that will be set in the Event registers.

■ Reading the Questionable Status Event register will reset it to zero.

■ The Questionable status Enable register can be programmed to specify the

questionable status event bit that is logically ORed to become Bit 3 (QUES bit) in the

Status Byte register.

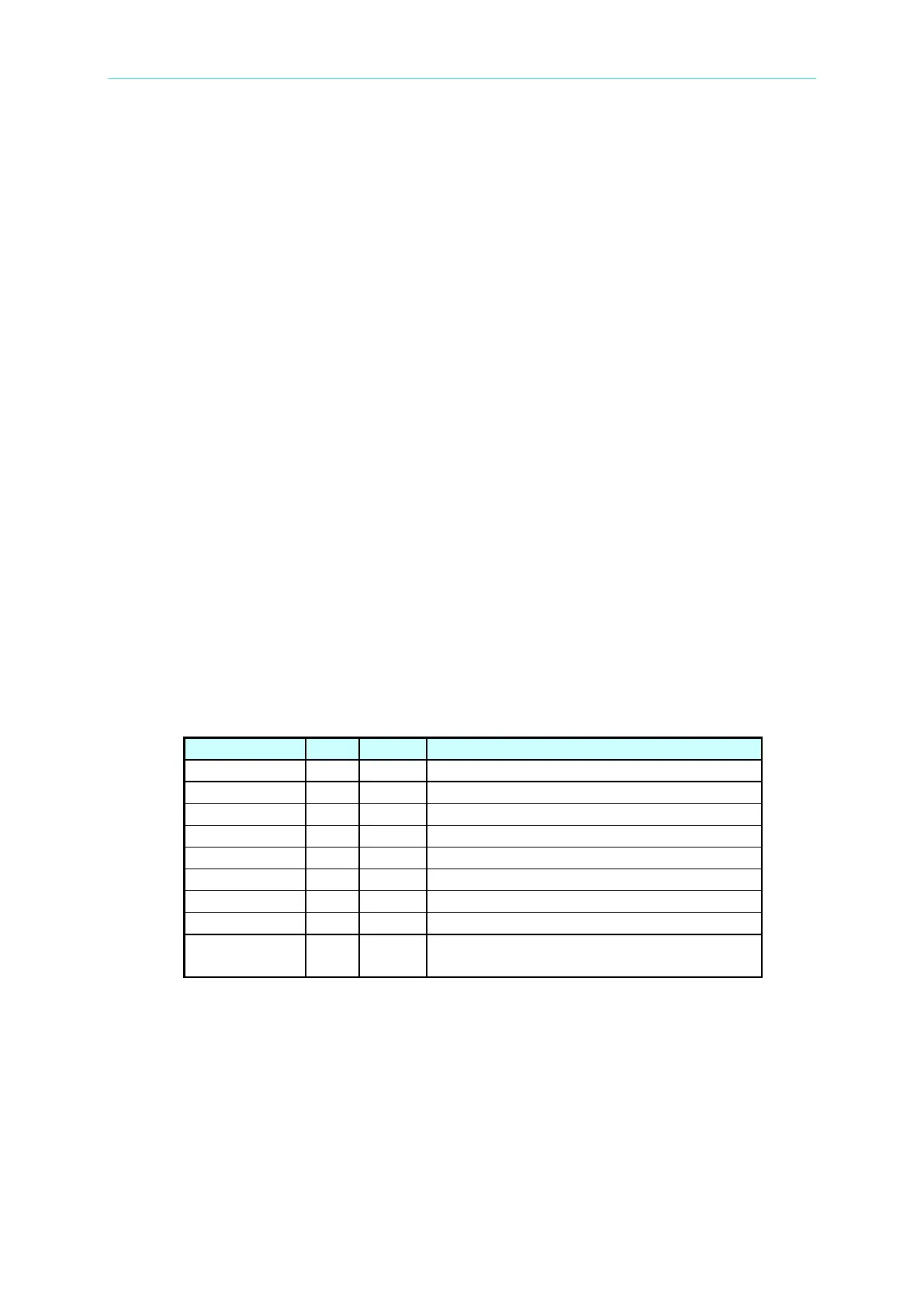

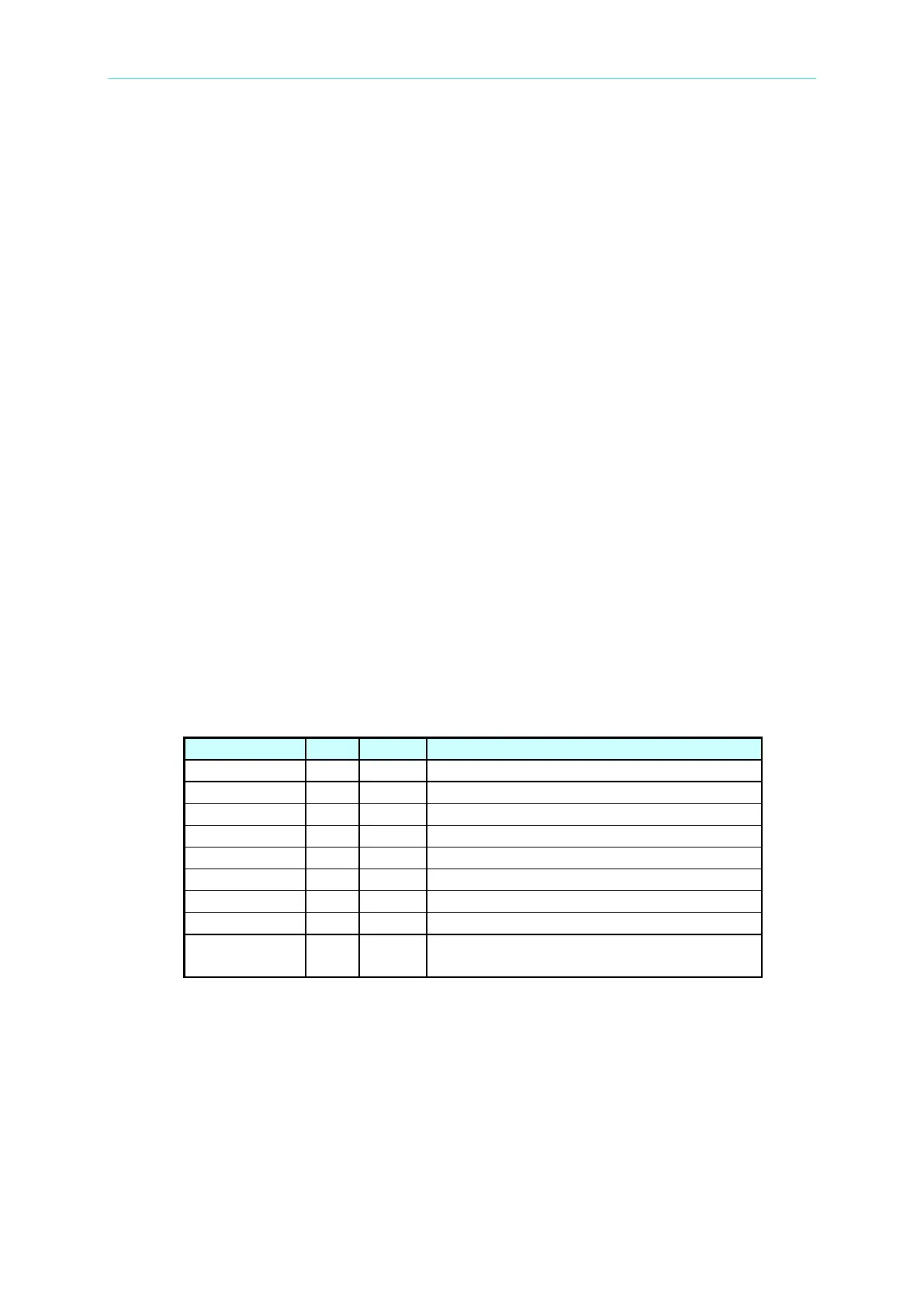

Table 5-2 Bit Description of Questionable Status

Temperature Error (Over temperature).

Current Error (Over current).

Power Error (Over power).

Reverse voltage on input.

Maximum sine wave current limit

Output Queue 5.2.4

■ The Output Queue stores output messages until they are read from the electronic load.

■ The Output Queue stores messages sequentially on a FIFO (First-In, First-Out) basis.

■ It sets to 4 (MAV bit) in the Status Byte register when there are data in the queue.

Loading...

Loading...