PROGRAMMABLE FREQUENCY DIVIDER

The programmable frequency divider uses a two modulus (divide number) prescaler

(U5, U6)

and two

programmable counters

(A

&

B). The prescaler is used to divide the

VCO

frequency down to a lower

frequency which can be handled by low power schottky TTL programmable counters. The two

mgdulus

prescaler permits prescaling without loss of resolution. At the start of the programmable frequency divider

cycle, the prescaler is set to divide by the larger modulus (41

),

and both programmable counters have been

loaded with their respective program numbers from the PIA. The programmable counters each

decrement 1 count for each output pulse from the prescaler. When programmable counter B

(U12, U13)

reaches the count of zero the 40141 control flip-flop (part of

Ul1)changes state and causes the prescaler to

divide by the lower modulus

(40). When programmable counter A reaches the count of

2

the

D

input of

the PL period flip-flop (part of

U11) goes high, so that on the count of 1 the flip-flop changes state, which

causes both programmable counters to be reloaded with their respective program numbers and the 40141

control flip-flop to reset (prescaler in

+

41 state). The very next count causes the PL period flip-flop to

reset, starting the programmable frequency divider cycle over again. The

equation3 or the divide ratio of

the programmable frequency divider

Nd

is:

Nd

=

40

(N counter A

)

+

N

counter

B

with the condition that:

counter B

exceed

counter A

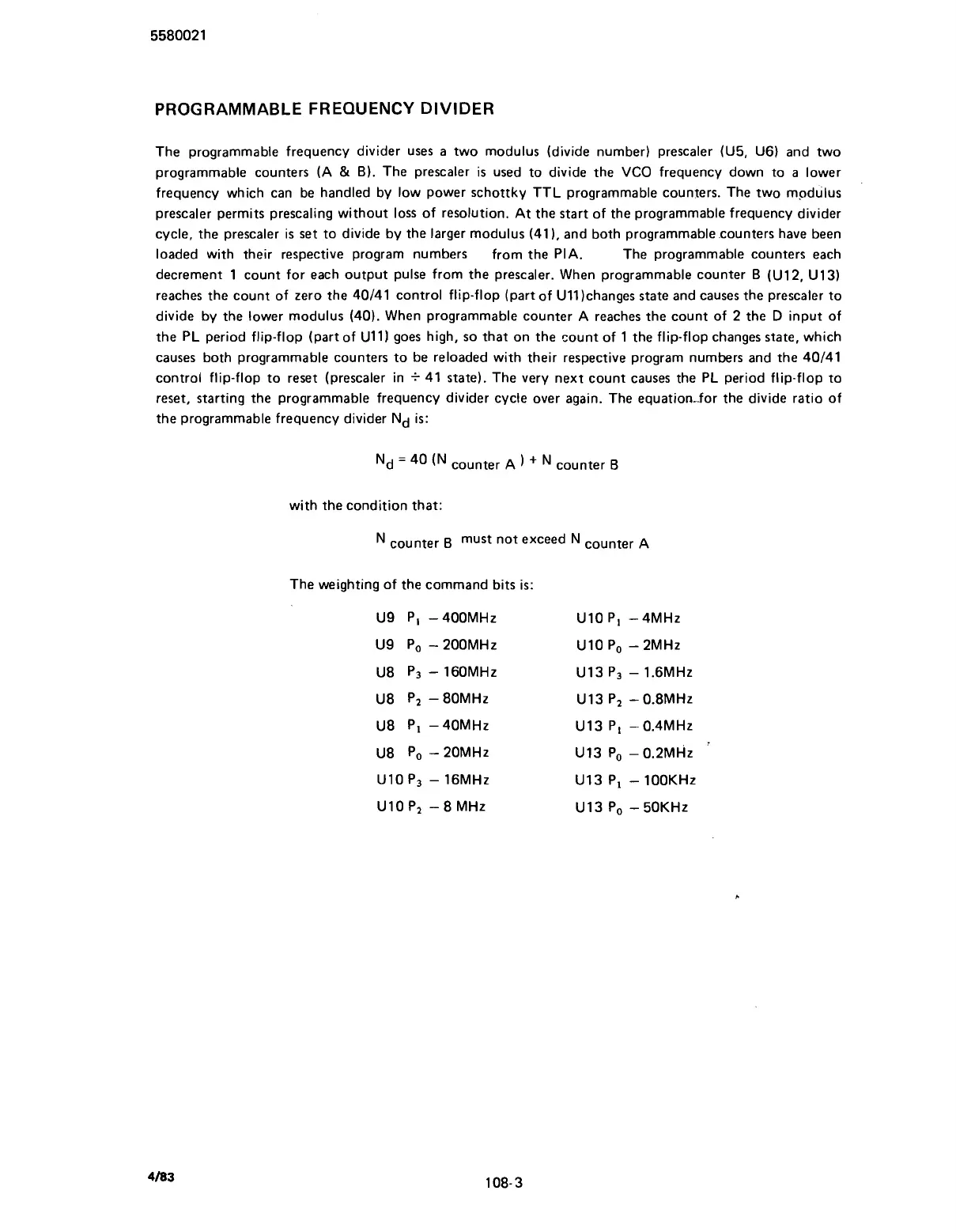

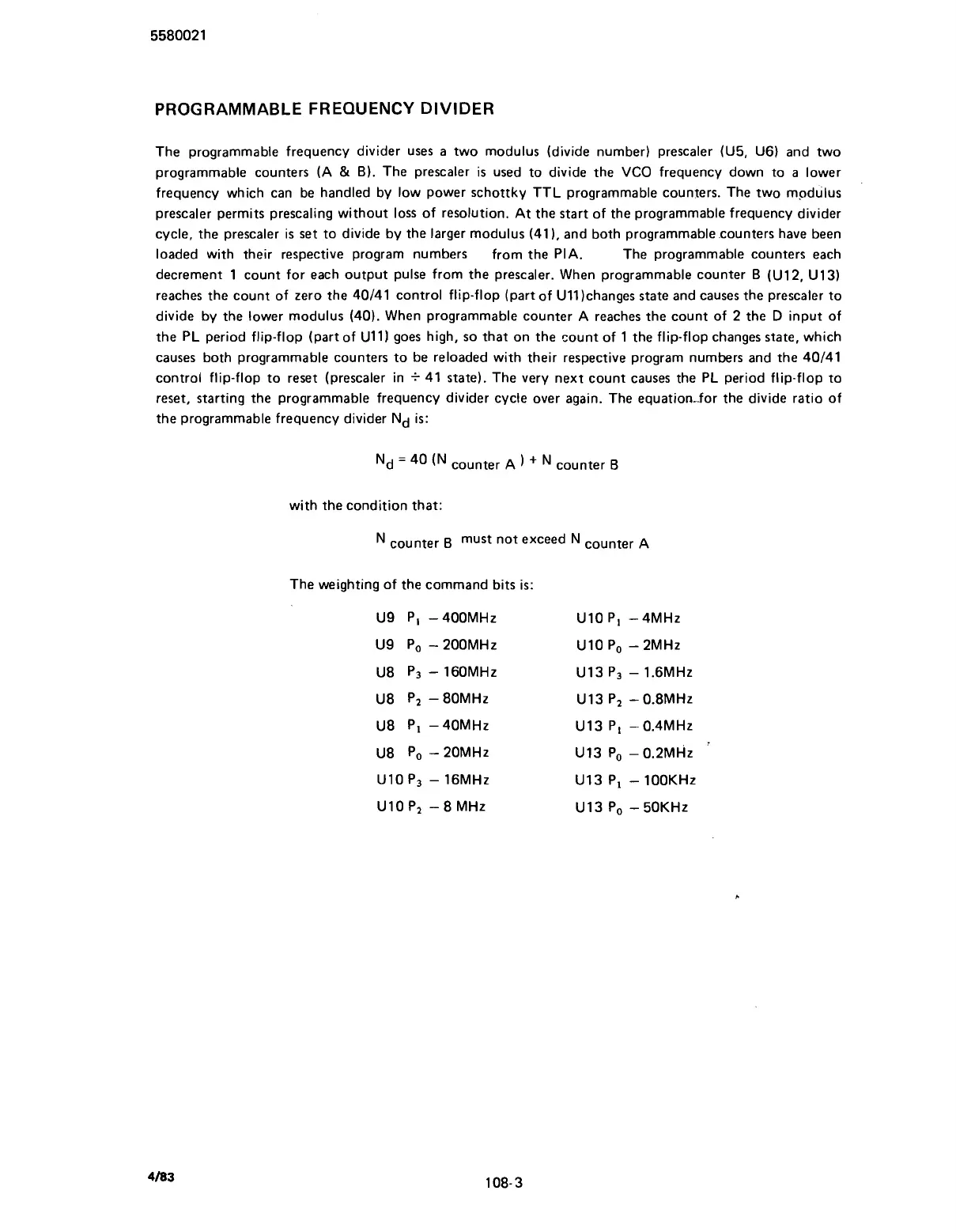

The weighting of the command bits is:

Scans by ArtekMedia © 2007

Loading...

Loading...