5700MSC-IP

IP Network Grand Master Clock & Video Master Clock System

Page - 28 Revision 0.2

3.2.5. Video Genlock Operation

The 5700MSC-IP can lock to various analog video sync references including NTSC, PAL, Slo-Pal

signals, and HD tri-level signals. The applied video reference type is auto detected. The full list of

supported standards is shown in Table 3-4. The lock behavior is described for each of the main video

sync types.

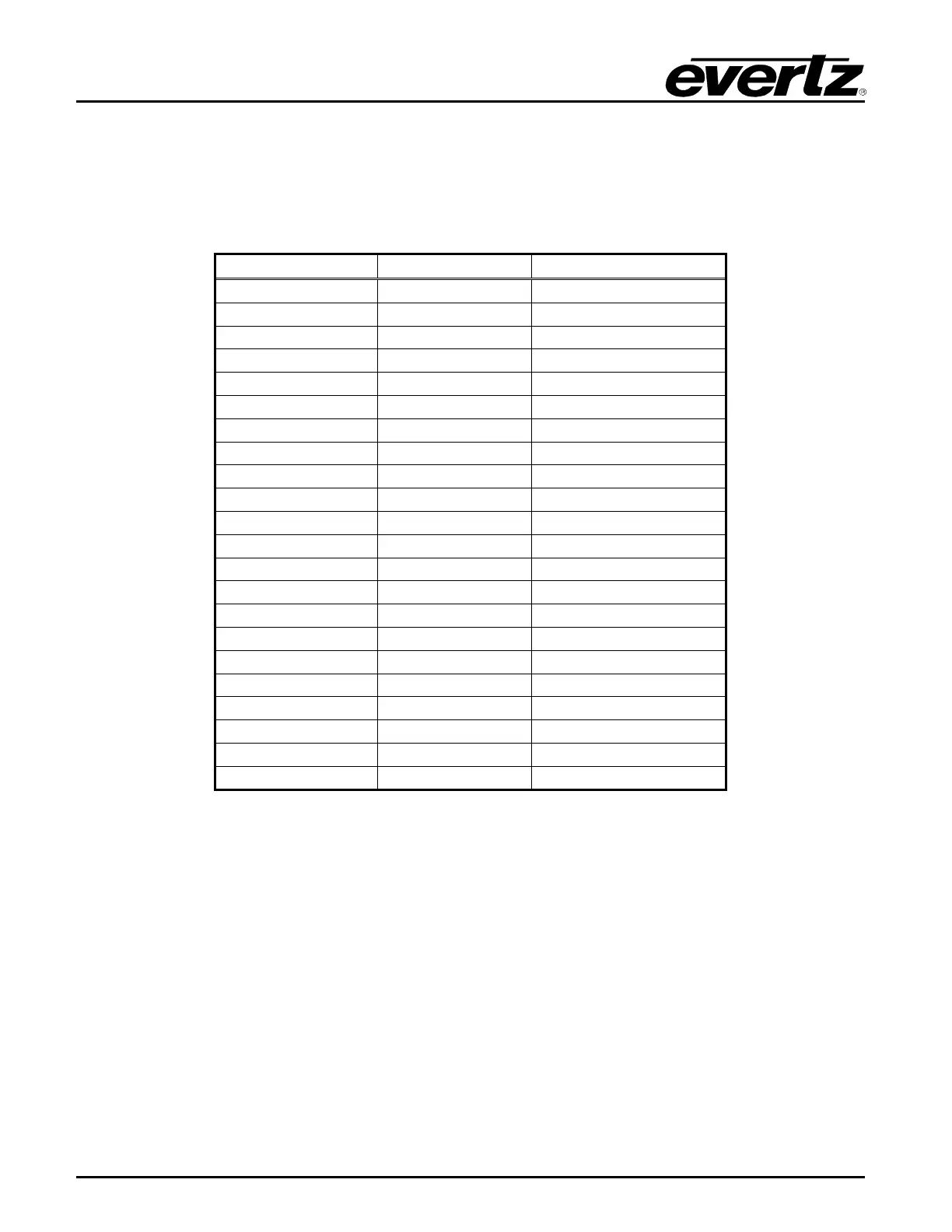

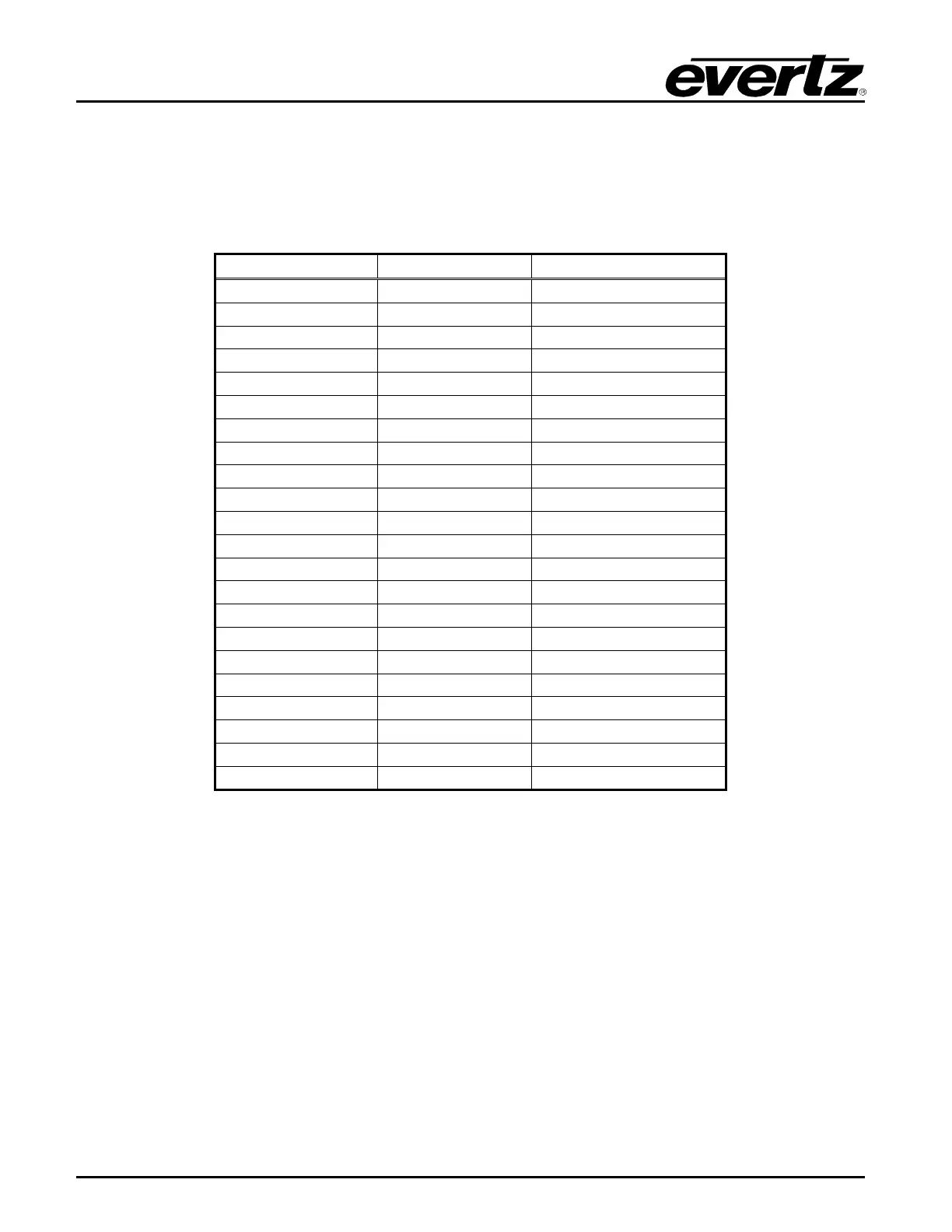

Table 3-4: Supported Analog Video Sync References

3.2.6. Serial Digital Video Timing

The 5700MSC-IP has four separate serial digital video test generators that can be phased

independently, and are also phased by the Global Phase controls. In all the supported standards, SD,

HD, and 3G, the video outputs are aligned to the supplied reference. The alignment to analog sync

has been calibrated using SMPTE compliant timing and is guaranteed to be accurate to within one

sample.

It should be noted that certain Tektronix equipment such as the WFM700 and WFM7120 will not show

correct alignment of a serial digital video source to a supplied external analog reference. These

devices appear to have been calibrated to the output of an unknown video DAC. This means they will

not display correct SMPTE timing due to the delay introduced in the measurements by the DAC

process. Since the outputs of the 5700MSC-IP are aligned using SMPTE timing, their phase must be

advanced significantly in order to appear correct with Tektronix timing.

Loading...

Loading...