5700MSC-IP

IP Network Grand Master Clock & Video Master Clock System

Page - 32 Revision 0.2

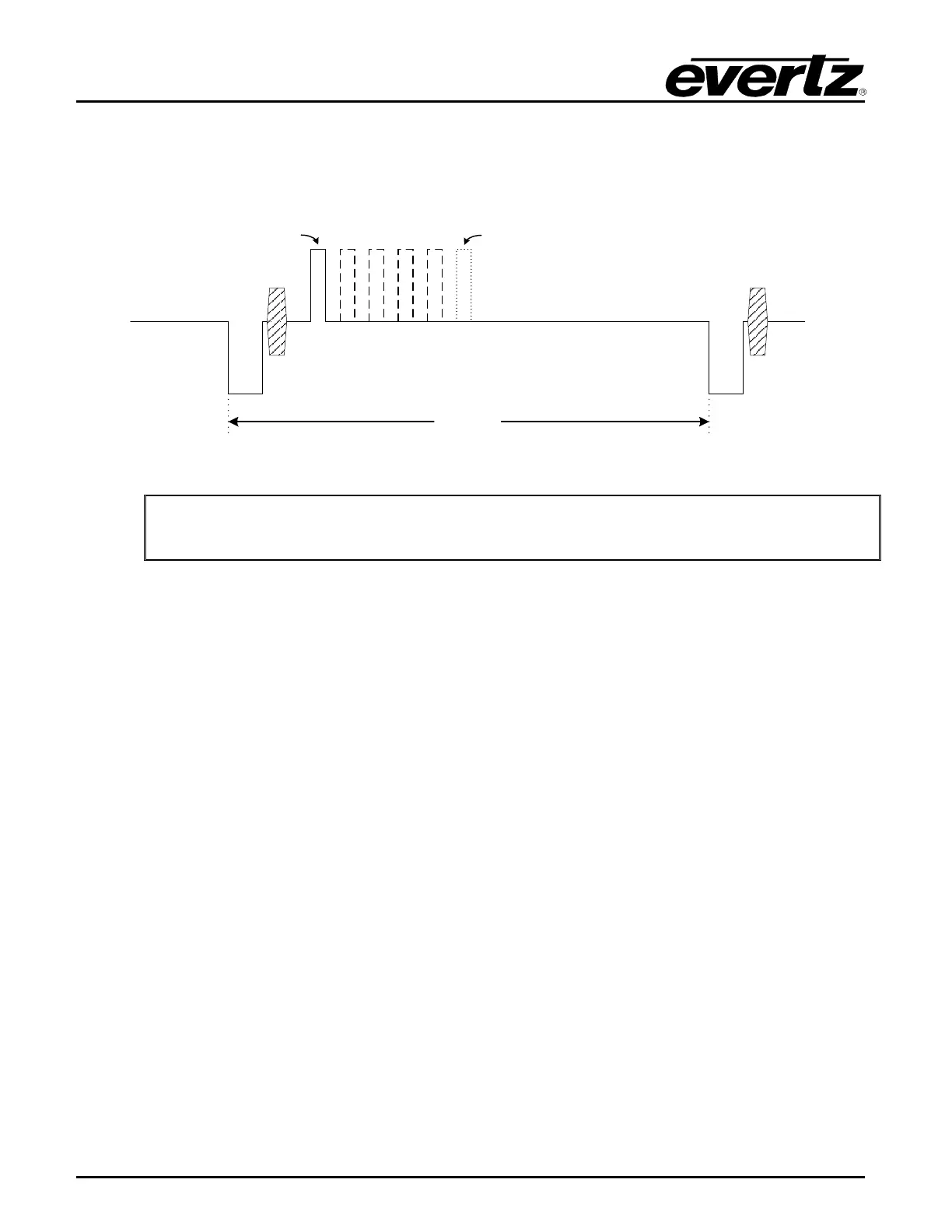

The SMPTE ST 318 ten-field reference can be generated by the 5700MSC-IP on any NTSC sync

output. It is turned on and off using the Ten Field Ctl menu item. The 10field waveform is illustrated

below in Figure 3-8. The number of pulses indicates where in the sequence the frame belongs. It is

inserted on lines 15 (field 1) and 278 (field 2).

Figure 3-8: SMPTE ST 318 Ten-field Reference on NTSC line 15

Note that AES/DARS Test Generator Outputs are only available on the +AUX option.

When the 5700MSC-IP is locked to an NTSC reference with a ten-field pulse, the AES, DARS, and

Wordclock outputs can be phase locked properly. The AES/DARS/WC lck menu item located in the

AES Audio menu off the OUTPUT root menu should be set to NTSC/fractional.

In the NTSC ten-field lock diagram above (Figure 3-7), the AES/DARS outputs are displayed as

frames. Each frame is divided into two subframes, labeled X and Y. The X subframe identifies channel

1 (left channel). The Y subframe identifies channel 2 (right channel). The wordclock output is high

during channel 1 and low during channel 2. Note that the AES/DARS and wordclock outputs can be

phased independently. If the phase of the AES/DARS outputs is changed for any reason, the phase of

the wordclock output should be changed as well to match.

The AES/DARS outputs provide a fixed sample rate of 48kHz (48,000 samples per second). This

means that during a single NTSC frame, 1601.6 AES frames will have been generated. It takes five

NTSC frames to fit a whole number of AES frames (8008 frames). This means that 48kHz AES/DARS

will line up evenly with NTSC sync once out of every five frames, and during the other four frames the

AES/DARS waveforms will appear to be partially shifted. The 10field sequence identifies frame #1 (a

single pulse) as the frame where the AES/DARS waveforms line up perfectly to horizontal sync of line

4 of the NTSC waveform. This is illustrated in lock diagram #2 (Figure 3-7).

Note that the Z preamble (which identifies the start of a 192-frame AES block) will only line up with

NTSC sync once every 120 frames (4.004 seconds). This is in contrast to PAL sync where it will line

up every frame. This essentially renders the AES Coarse phase adjustment meaningless when locked

to an NTSC reference. The alignment of an AES block to analog video sync is not important for proper

reception of an AES signal.

If the NTSC reference is lost, the unit will freerun on the selected oscillator. Note than when the

Genlock Range is set to Wide, the freerun drift upon loss of reference will be much higher. When the

NTSC reference is re-applied the Lock Type menu selection controls how the 5700MSC-IP will

respond to re-align its internal oscillator with the reference.

2 3 4 5

Start Pulse

Field2 Pulse

Line 15

1

Loading...

Loading...