20 IBM System x3850 X6 and x3950 X6 Planning and Implementation Guide

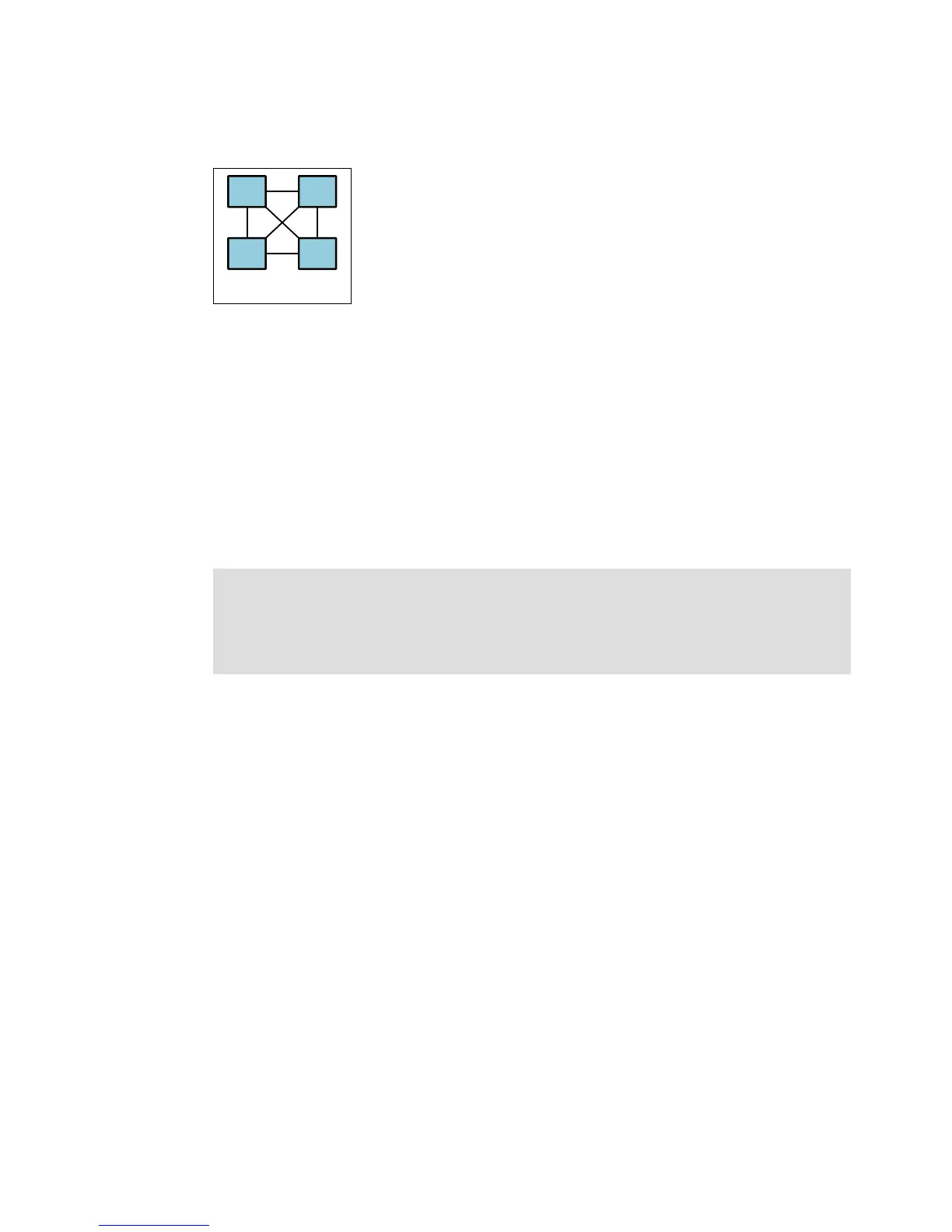

Figure 2-13 shows how the four processors of the x3850 X6 are connected via QPI links. In

this configuration, each processor is directly connected to all other processors.

Figure 2-13 QPI links between processors

In the Compute Book, each processor has four Scalable Memory Interconnect Generation 2

(SMI2) channels (two memory controllers per processor, each with two SMI channels) that

are connected to four scalable memory buffers. Each memory buffer (MB) has six DIMM slots

(two channels with three DIMMs per channel) for a total of 24 DIMMs (eight channels with

three DIMMs per channel) per processor. Compute Books are connected to each other via

Quick Path Interconnect (QPI) links.

The Primary I/O Book has three PCIe 3.0 slots, Mezzanine LOM slot, I/O Controller Hub,

Integrated Management Module II (IMM2) and peripheral ports (such as USB, video, serial)

on the board. Additional I/O Books (Full-length and Half-length) have three PCIe 3.0 slots

each and provide ability to hot-add and hot-remove PCIe adapters.

The Primary I/O Book is connected to the Compute Books 1 (CPU 1) and 2 (CPU 2) directly

via PCIe links from those processors: PCIe slots 9 and 10 are connected to CPU 1, and PCIe

slots 7 and 8 are connected to CPU 2. Also, both CPU 1 and CPU 2 are connected to the Intel

I/O Hub via Direct Media Interface (DMI) switched links for redundancy purposes.

The Storage Book is also connected to both Compute Books 1 and 2, however, the PCIe slots

11 and 12 are connected to different processors (CPU 2 and CPU 1 respectively). In addition,

certain peripheral ports are routed from the Intel I/O Hub and IMM2 to the Storage Book.

Additional I/O Books are connected to Compute Books 3 and 4 and use PCIe links from

CPU 3 and CPU 4. If you need to install additional I/O Books, you should install the Compute

Book in an appropriate slot first.

The System x3850 X6 server is designed so that it can tolerate the failure of CPU 1. This

feature decreases downtime in the event of a processor failure, and it requires two Compute

Books installed in Compute Book slots 1 and 2, and an OS boot path from the CPU in

Compute Book 2. Downtime is decreased by allowing the machine to boot on another

processor until time can be taken to engage IBM service.

When the server detects a failure of CPU 1, the IMMv2 reroutes the Intel I/O Hub to CPU 2

instead. The system will boot using CPU 2, albeit with reduced functionality. This failover to a

surviving processor is automatic and is handled by the system at boot time.

Additional I/O Books: For illustration purposes, both Half-length and Full-length I/O

Books are shown in Figure 2-12, where the Half-length I/O Book supplies slots 1, 2, and 3,

and the Full-length I/O Book supplies slots 4, 5, and 6. The Half-length I/O Book can also

be used to supply slots 4, 5, and 6, and the Full-length I/O Book can also be used to supply

slots 1, 2, and 3.

4 3

21

x3850 X6 - 4 sockets

Loading...

Loading...