Chapter 2. Technology 37

The algorithm uses short and long term thresholds per memory rank with leaky bucket and

automatic sorting of memory pages with the highest correctable error counts. First, it

leverages hardware recovery features, followed by software recovery features, to optimize

recovery results for both newer and older operating systems and hypervisors.

When recovery features are exhausted, firmware will issue a Predictive Failure Alert. Memory

which has failed completely will be held offline during reboots until repaired. Failed DIMMs are

indicated by light path diagnostics LEDs physically at the socket location.

IBM performs thorough testing to verify the features and co-ordination between the firmware

and the operating system or hypervisor.

2.5 PCIe 3.0

The X6 family servers supports the new generation of PCI Express (PCIe) protocol, Version

3.0. PCIe 3.0 is the evolution of PCI Express I/O standard which brings doubled bandwidth

over PCIe 2.0, preserving compatibility with previous generations of PCIe protocol. That

means PCIe 1.x and 2.x cards will properly work in PCIe 3.0-capable slots, and PCIe 3.0

cards will work when plugged into PCIe slots of previous generations.

PCIe 3.0 uses a 128b/130b encoding scheme, which is more efficient than the 8b/10b

encoding used in PCIe 2.0 protocol. This approach reduces overhead to less that 2%

comparing to 20% of PCIe 2.0, and allows you to double bandwidth at 8 GT/s speed.

Each Intel Xeon E7-4800/8800 v2 processor contains an Integrated I/O (IIO) module that

provides 32 lanes of PCIe 3.0. These 32 lanes can be split into any combination of x4, x8,

and x16.

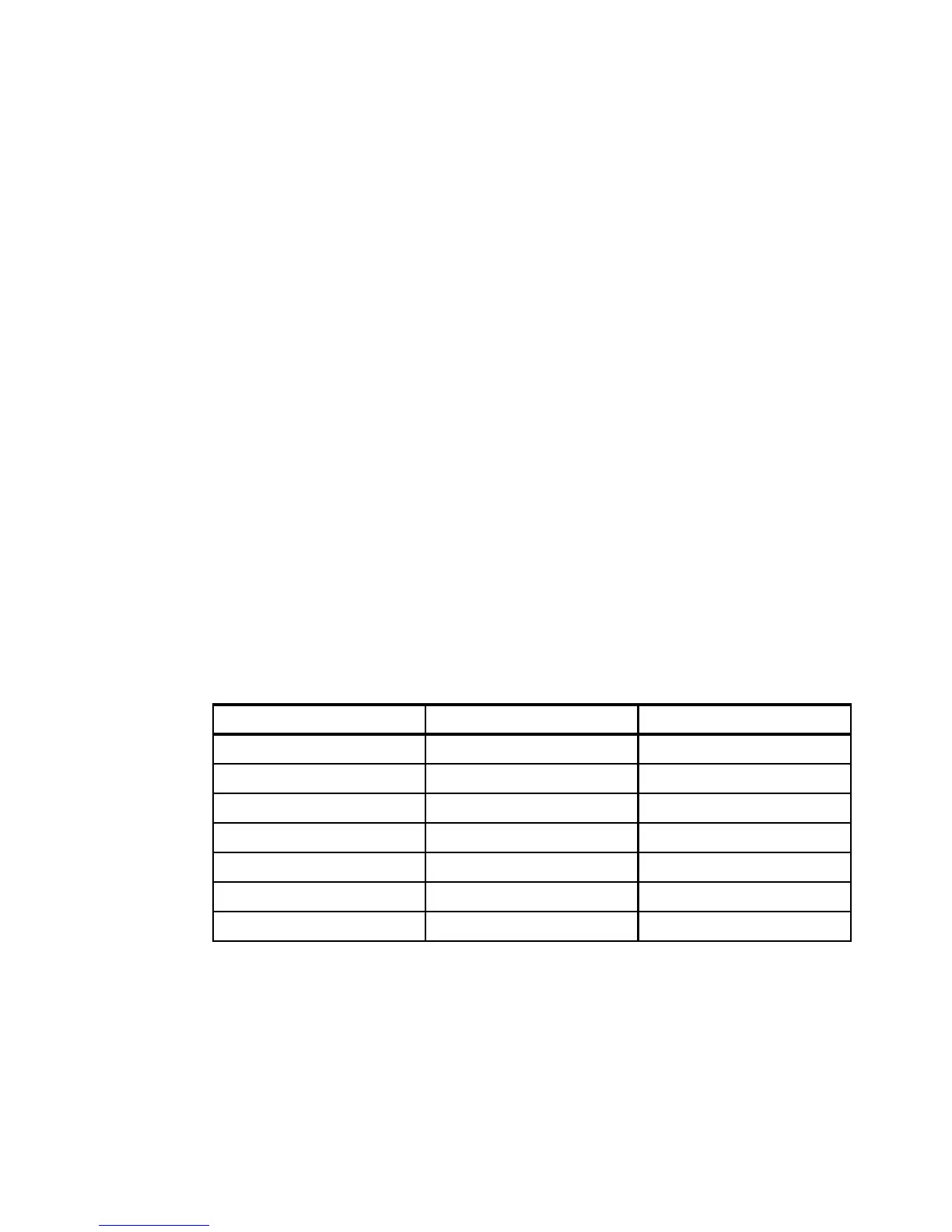

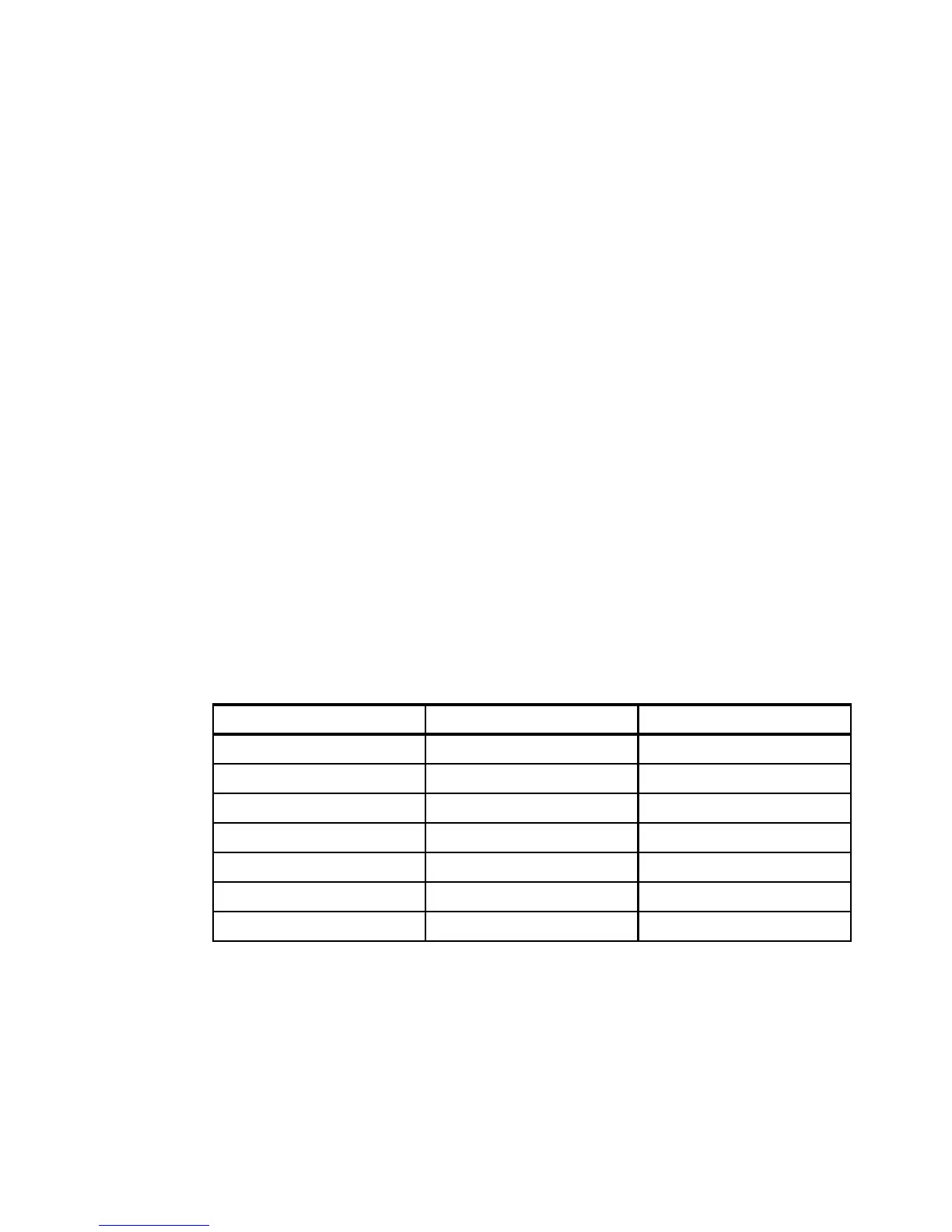

Table 2-3 shows a comparison of the PCIe capabilities of the eX5 and X6 families.

Table 2-3 X5 and X6 PCIe capabilities comparison

For additional information about PCIe 3.0, see the PCI Express Base 3.0 specification by

PCI-SIG. It can be found at the following web page:

http://www.pcisig.com/specifications/pciexpress/base3/

We describe the details about the implementation of the I/O subsystem in Chapter 3, “Product

information” on page 47

Specification x3850 X5 x3850 X6

PCIe version PCIe 2.0 PCIe 3.0

Raw bit rate 5 GT/s 8 GT/s

Encoding 8b/10b 128b/130b

Bandwidth per lane ~500 MB/s ~1 GB/s

Available PCIe slots 8 12

Number of x16 slots 1 Up to 6

a

a. 6 PCIe x16 slots are available for configurations with two full-length I/O Books

Hot-swap support No Yes

b

b. Hot-swap capabilities are available only for additional I/O Books.

Loading...

Loading...