Chapter 2. Technology 19

For more information about the additional power supplies, see 3.22, “Power subsystem” on

page 101.

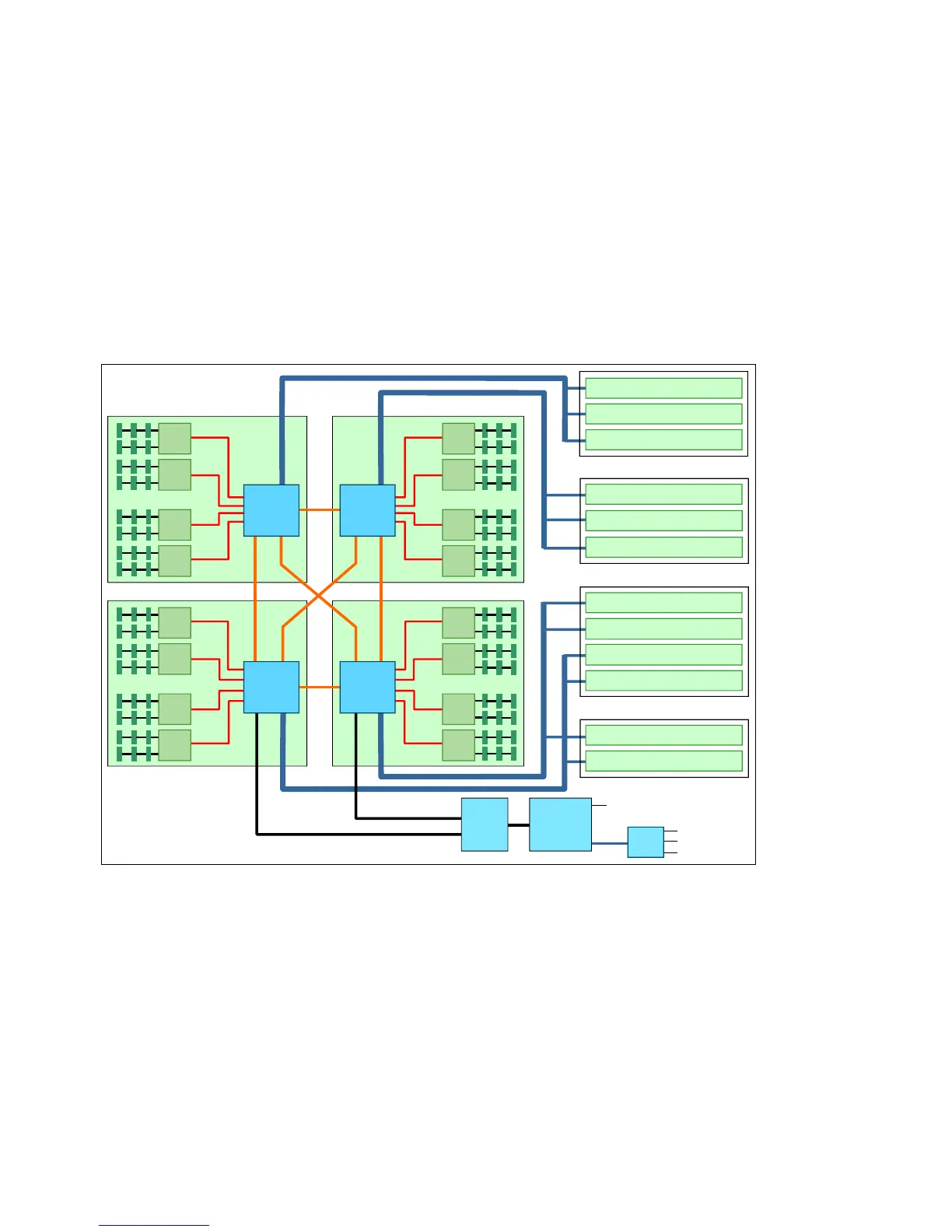

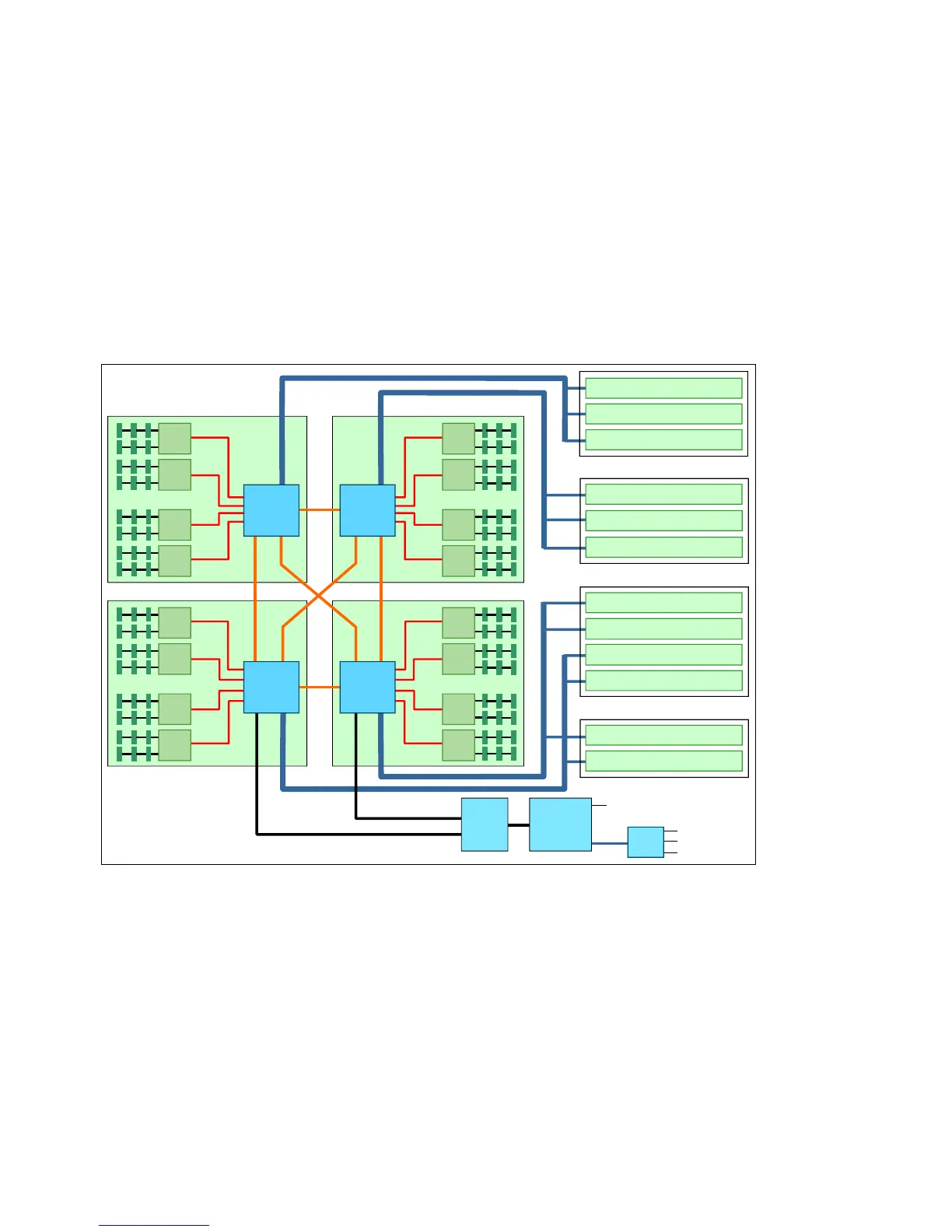

2.2 System architecture

This section shows the overall architecture of both the x3850 X6 and x3950 X6.

2.2.1 x3850 X6

Figure 2-12 shows the system architecture of the x3850 X6 server.

Figure 2-12 x3850 X6 system architecture

Processor-to-processor communication is carried over shared-clock or coherent quick path

interconnect (QPI) links. Each processor has three QPI links to connect to other processors.

SMI

links

MB 2

MB 1

X6 DDR3

Compute Book

QPI links

Intel

Xeon

CPU 1

MB 2

MB 1

MB 2

MB 1

MB 2

MB 1

MB 2

MB 1

DMI

links

Slot 7: PCIe 3.0 x16 (x16)

Slot 9: PCIe 3.0 x16 (x16)

MB 2

MB 1

MB 2

MB 1

MB 2

MB 1

8x USB

Serial

Management

Video

IMM2

PCIe x1

Slot 10: Mezz LOM (x8)

Slot 12: PCIe 3.0 x16 (x8)

Intel

Xeon

CPU 2

Slot 8: PCIe 3.0 x16 (x8)

Slot 11: PCIe 3.0 x16 (x8)

Intel

Xeon

CPU 4

Intel

Xeon

CPU 3

Slot 1: PCIe 3.0 x16 (x16)

Slot 2: PCIe 3.0 x8 (x8)

Slot 3: PCIe 3.0 x8 (x8)

Slot 4: PCIe 3.0 x16 (x16)

Slot 5: PCIe 2.0 x8 (x8)

Slot 6: PCIe 3.0 x16 (x16)

Storage Book

Primary I/O Book

PCIe 3.0 lanes

Full Length I/O Book

Half Length I/O Book

PCIe 3.0 lanes

Intel

I/O Hub

PCIe

switch

Loading...

Loading...