22 IBM System x3850 X6 and x3950 X6 Planning and Implementation Guide

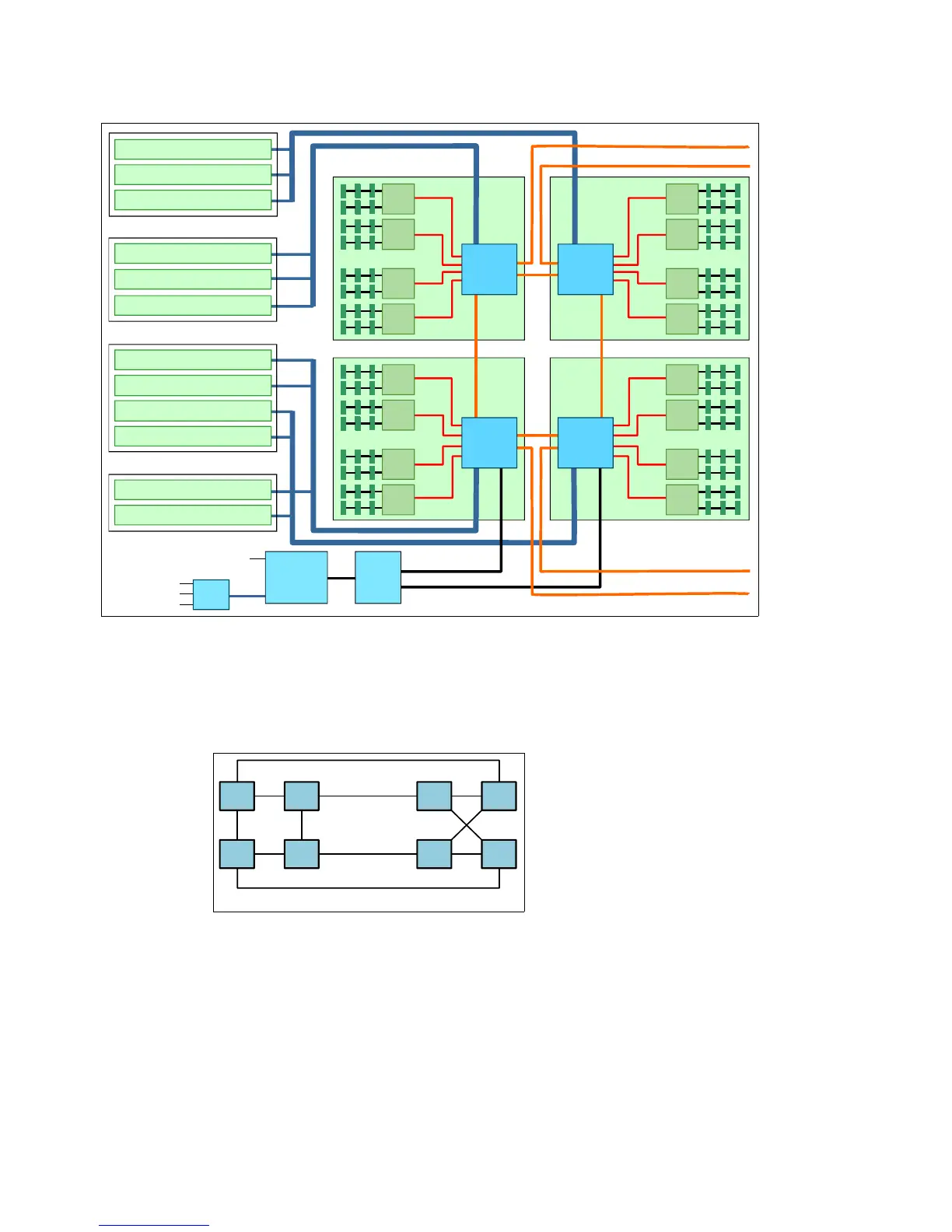

Figure 2-15 x3950 X6 system architecture (top half)

The 8-socket configuration is formed using the native QPI scalability of the Intel Xeon

processor E7 family.

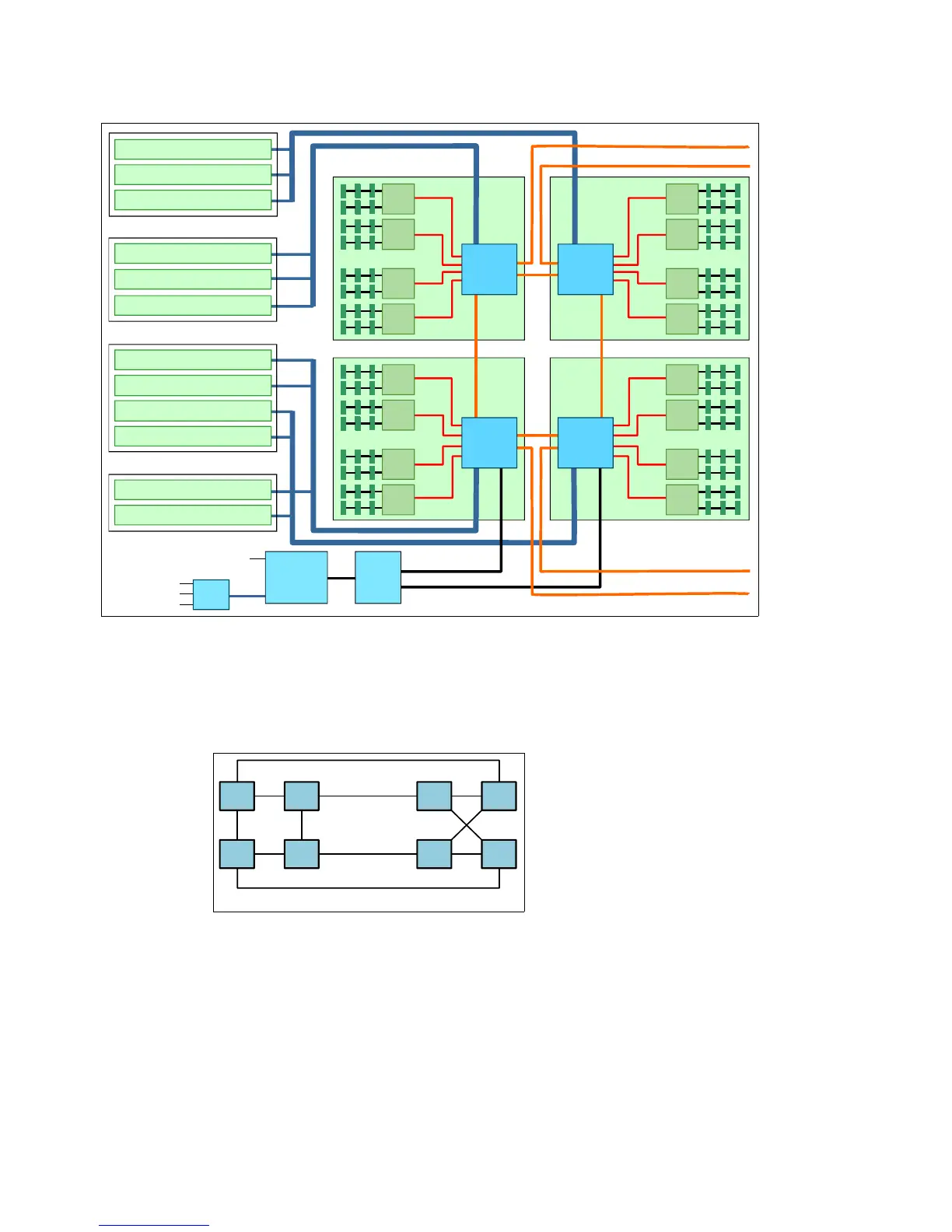

Figure 2-16 shows how the processors are connected together using QPI links.

Figure 2-16 QPI connectivity - x3950 X6 with 8 processors installed

SMI

links

MB 2

MB 1

X6 DDR3

Compute Book

QPI links

MB 2

MB 1

MB 2

MB 1

MB 2

MB 1

MB 2

MB 1

DMI links

Slot 39: PCIe 3.0 x16 (x16)

Slot 41: PCIe 3.0 x16 (x16)

MB 2

MB 1

MB 2

MB 1

MB 2

MB 1

8x USB

Serial

Management

Video

IMM2

PCIe x1

Slot 42: Mezz LOM (x8)

Slot 44: PCIe 3.0 x16 (x8)

Slot 40: PCIe 3.0 x16 (x8)

Slot 43: PCIe 3.0 x16 (x8)

Slot 33: PCIe 3.0 x16 (x16)

Slot 34: PCIe 3.0 x8 (x8)

Slot 35: PCIe 3.0 x8 (x8)

Slot 36: PCIe 3.0 x16 (x16)

Slot 37: PCIe 2.0 x8 (x8)

Slot 38: PCIe 3.0 x16 (x16)

Storage Book

Primary I/O Book

PCIe 3.0 lanes

Full Length I/O Book

Half Length I/O Book

PCIe 3.0 lanes

QPI link (to CPU 2)

QPI link (to CPU 3)

QPI link (to CPU 4)

QPI link (to CPU 1)

PCIe

switch

Intel

I/O Hub

Intel

Xeon

CPU 7

Intel

Xeon

CPU 8

Intel

Xeon

CPU 5

Intel

Xeon

CPU 6

4 3

21

7 8

56

x3950 X6 - 8 sockets

Loading...

Loading...