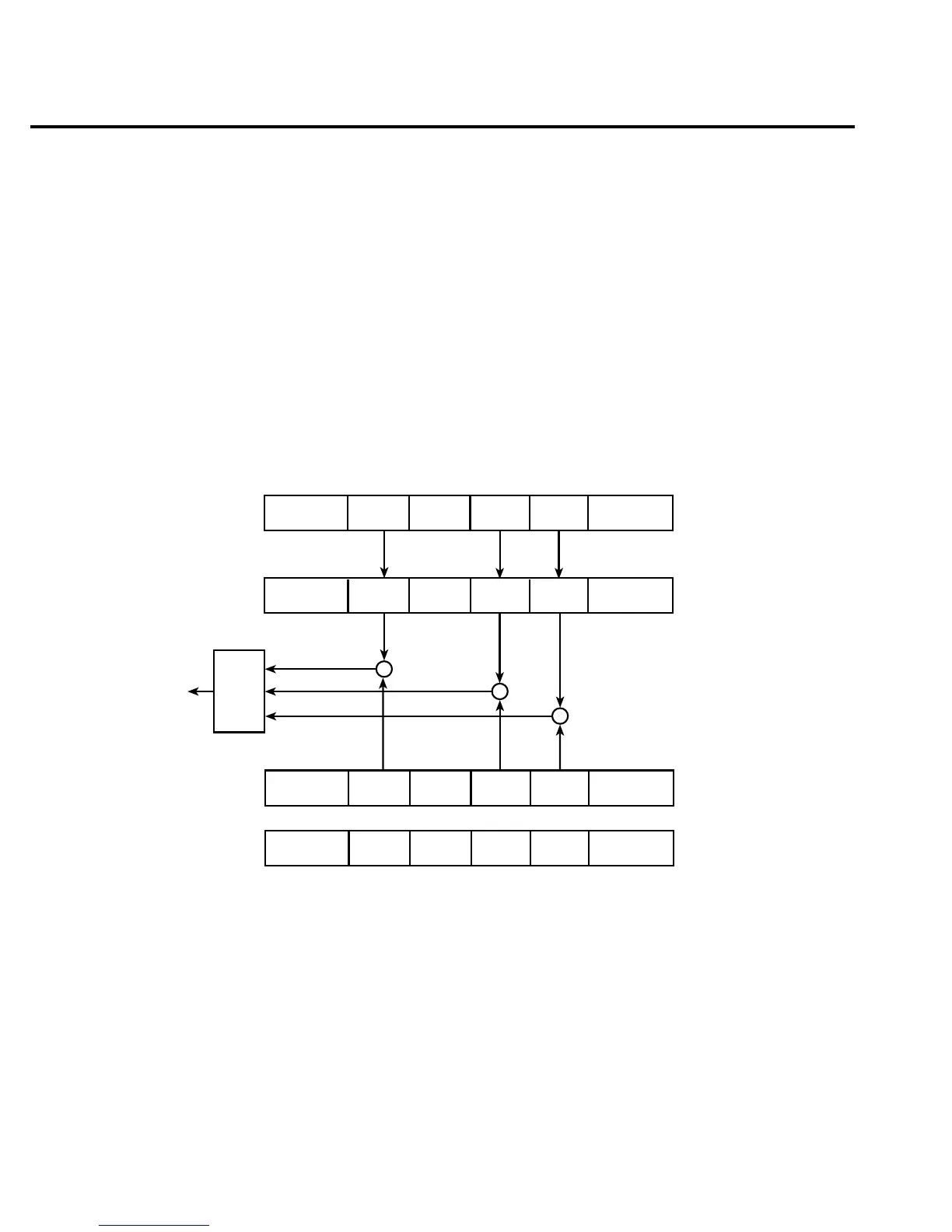

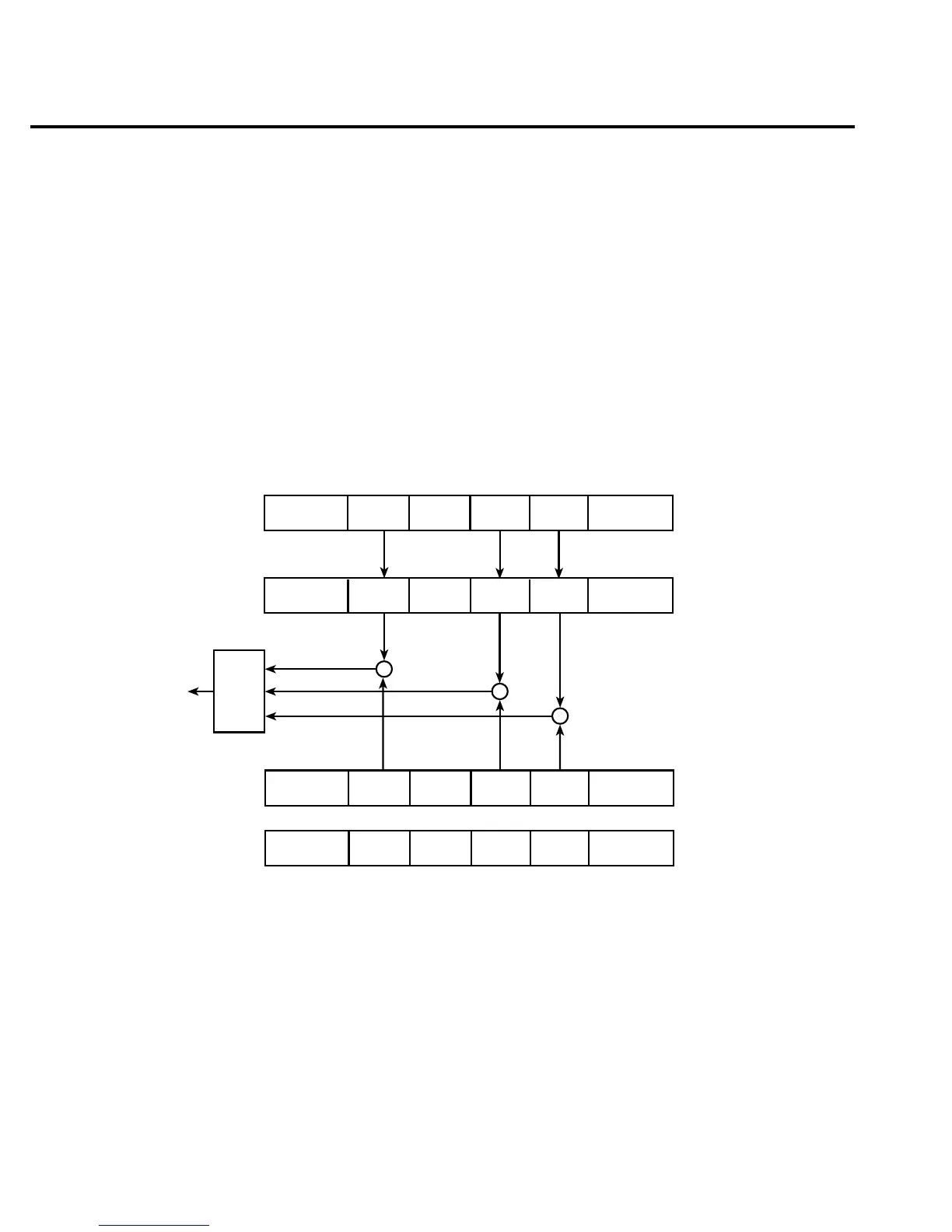

7-12 Status Structure

Operation event status

The used bits of the operation event register (shown in Figure 7-5) are described as follows:

• Bit B3, current limit (CL) — Set bit indicates that the output is in current limit. This

bit clears when the instrument is no longer in current limit.

• Bit B4, current limit tripped (CLT) — Set bit indicates that the output has turned off

due to a current limit condition. This bit clears when the output is turned back on.

• Bit B6, power supply shutdown (PSS) — This bit indicates that the output has turned

off due to an overload and/or overheat condition. This typically indicates that the user

tried to exceed the power output capability of the unit.

___

PSS

___

CLT

CL

___

(B15-B7)

(B6)

(B5)

(B4)

(B3)

(B2-B0)

OR

&

&

&

:CONDition?

[:EVENt]?

To OPC bit

of Status Byte

Register

:ENABle <NRf>

:ENABle?

Decimal Weights

Operation Condition

Register

Operation Event

Register

PSS = Power Supply Shutdown

CLT = Current Limit Tripped

& = Logical AND

OR = Logical OR

___

PSS

___

CLT

CL

___

(B15-B7)

(B6)

(B5)

(B4)

(B3)

(B2-B0)

___

PSS

___

CLT

CL

___

(B15-B7)

(B6)

(B5)

(B4)

(B3)

(B2-B0)

___

64

___

16

8

___

(2

6

)

(2

4

)

(2

3

)

Operation Event

Enable Register

CL = Current Limit

Figure 7-5

Operation event status

Loading...

Loading...