Status Structure 7-15

Condition registers

As Figure 7-1 shows, each status register set (except the standard event register set) has a con-

dition register. A condition register is a real-time, read-only register that constantly updates to

reflect the present operating conditions of the instrument. For example, when a current pulse is

not detected, bit B4 (PTT) of the measurement condition register will be set (1). When the pulse

is detected, the bit clears (0).

The commands to read the condition registers are listed in Table 7-3. For details on reading

registers, see “Reading registers”.

Event registers

As Figure 7-1 shows, each status register set has an event register. When an event occurs, the

appropriate event register bit sets to 1. The bit remains latched to 1 until the register is reset.

Reading an event register clears the bits of that register. *CLS resets all four event registers.

The commands to read the event registers are listed in Table 7-4. For details on reading reg-

isters, see “Reading registers”.

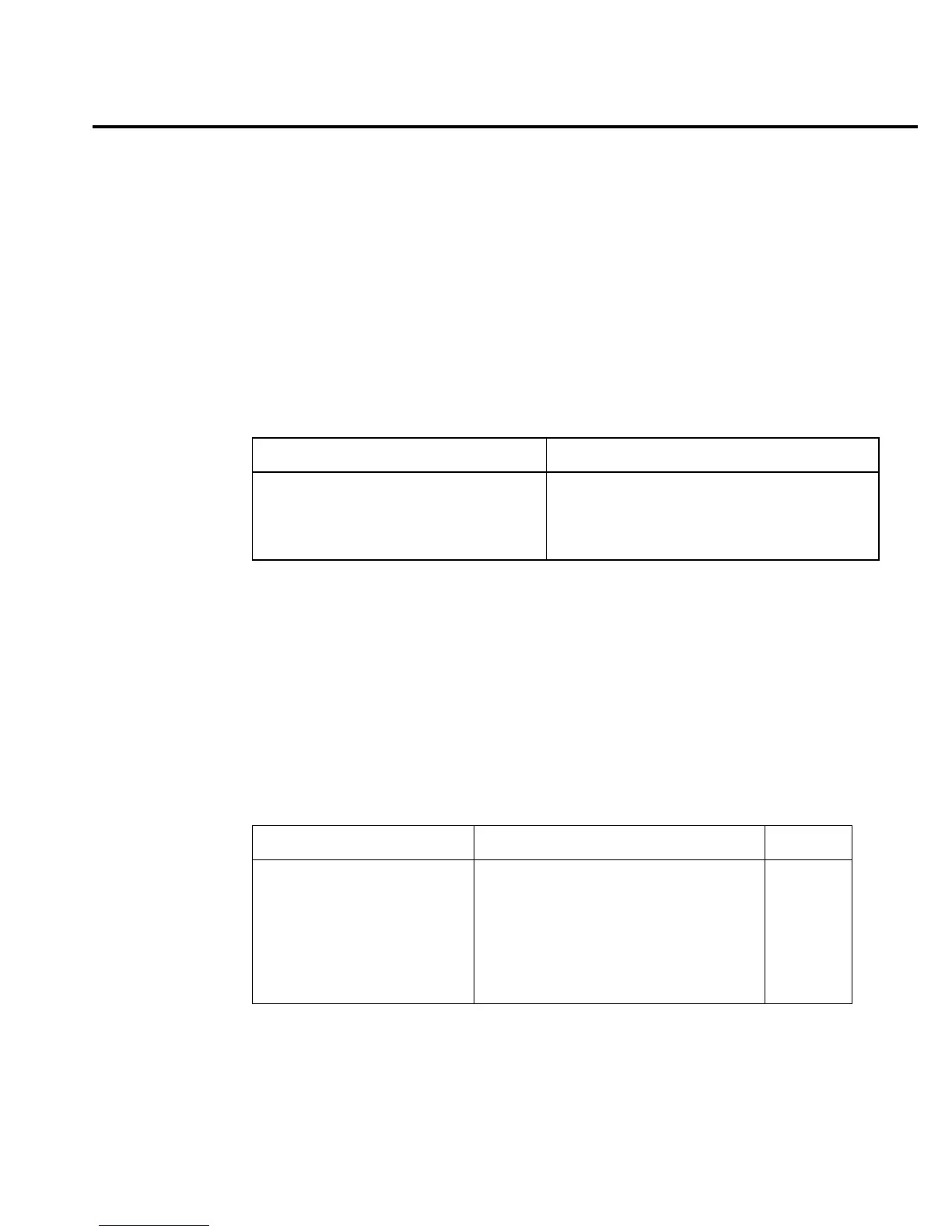

Table 7-3

Common and SCPI commands — condition registers

Command Description

STATus

:OPERation:CONDition?

:MEASurement:CONDition?

:QUEStionable:CONDition?

STATus subsystem:

Read operation condition register.

Read measurement condition register.

Read questionable condition register.

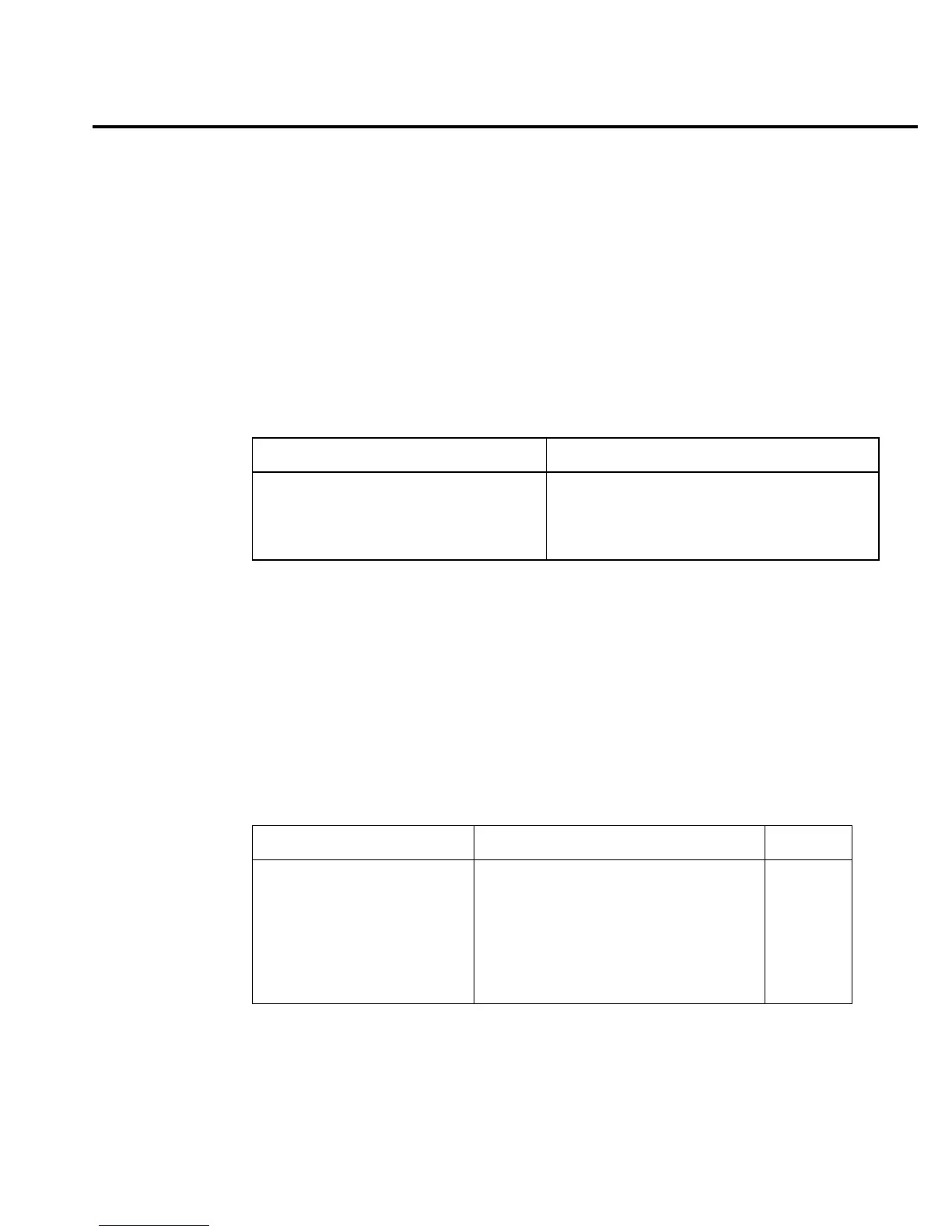

Table 7-4

Common and SCPI commands — event registers

Command Description Default

*ESR? Read standard event status register.

(Note)

STATus

:OPERation:[:EVENt]?

:MEASurement:[:EVENt]?

:QUEStionable:[:EVENt]?

STATus subsystem:

Read operation event register.

Read measurement event register.

Read questionable event register.

Note: Power-up and *CLS resets all bits of all event registers to 0. STATus:PRESet has no effect.

Loading...

Loading...