Configuration CP308

Page 4 - 20 ID 1027-4487, Rev. 3.0

P R E L I M I N A R Y

4.4 SMC-Specific Registers

The following registers are special registers which the CP308 uses to monitor and configure

the System Management Controller.

4.4.1 SMC Controller Status Register 0 (ICSTA0)

The SMC Controller Status Register 0 holds the bit for selecting the SPI Flash and provides

status information about basic reset and power management settings from the SMC controller.

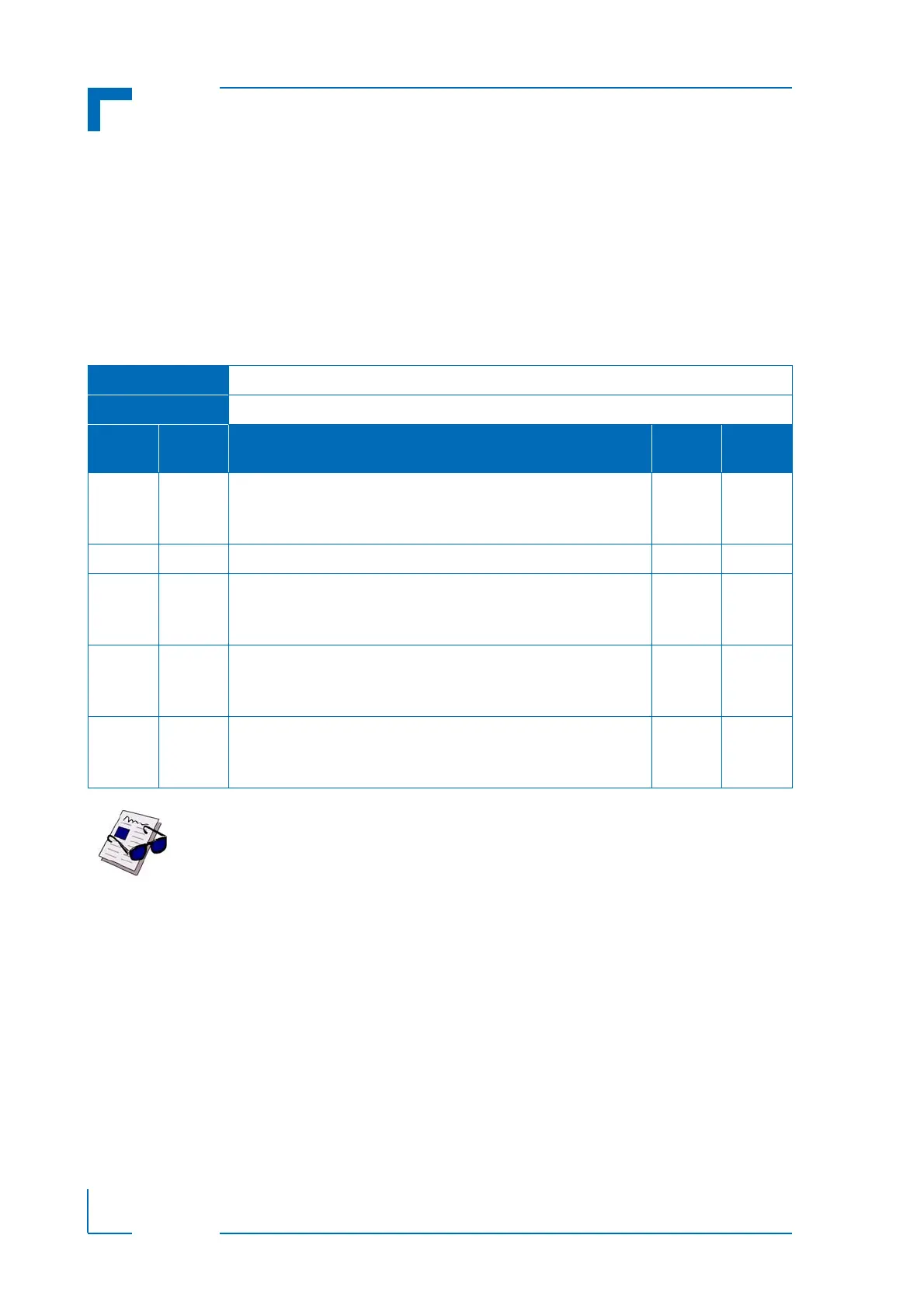

Table 4-20: SMC Controller Status Register 0 (ICSTA0)

REGISTER NAME SMC CONTROLLER STATUS REGISTER 0 (ICSTA0)

ADDRESS 0x29D

BIT NAME DESCRIPTION

RESET

VALUE

ACCESS

7 HFSEL SPI boot Flash selection:

0 = Select default boot Flash device

1 = Select alternative boot Flash device

0R

6 - 3 Res. Reserved 0000 R

2 HPWRB Power button signal to chipset:

0 = No power button signal to the chipset

1 = Power button signal generated to the chipset

0R

1 HRST Host reset (edge-sensitive reset):

0 = No host reset

1 = Host reset generated

0R

0 HPGD Power-on host reset (cold reset / level-sensitive reset):

0 = No power-on host reset

1 = Power-on host reset generated

0R

Note ...

This register can be configured only by the SMC controller and is set to the

default values by power-on reset, not by PCI reset.

Loading...

Loading...