Configuration CP308

Page 4 - 10 ID 1027-4487, Rev. 3.0

P R E L I M I N A R Y

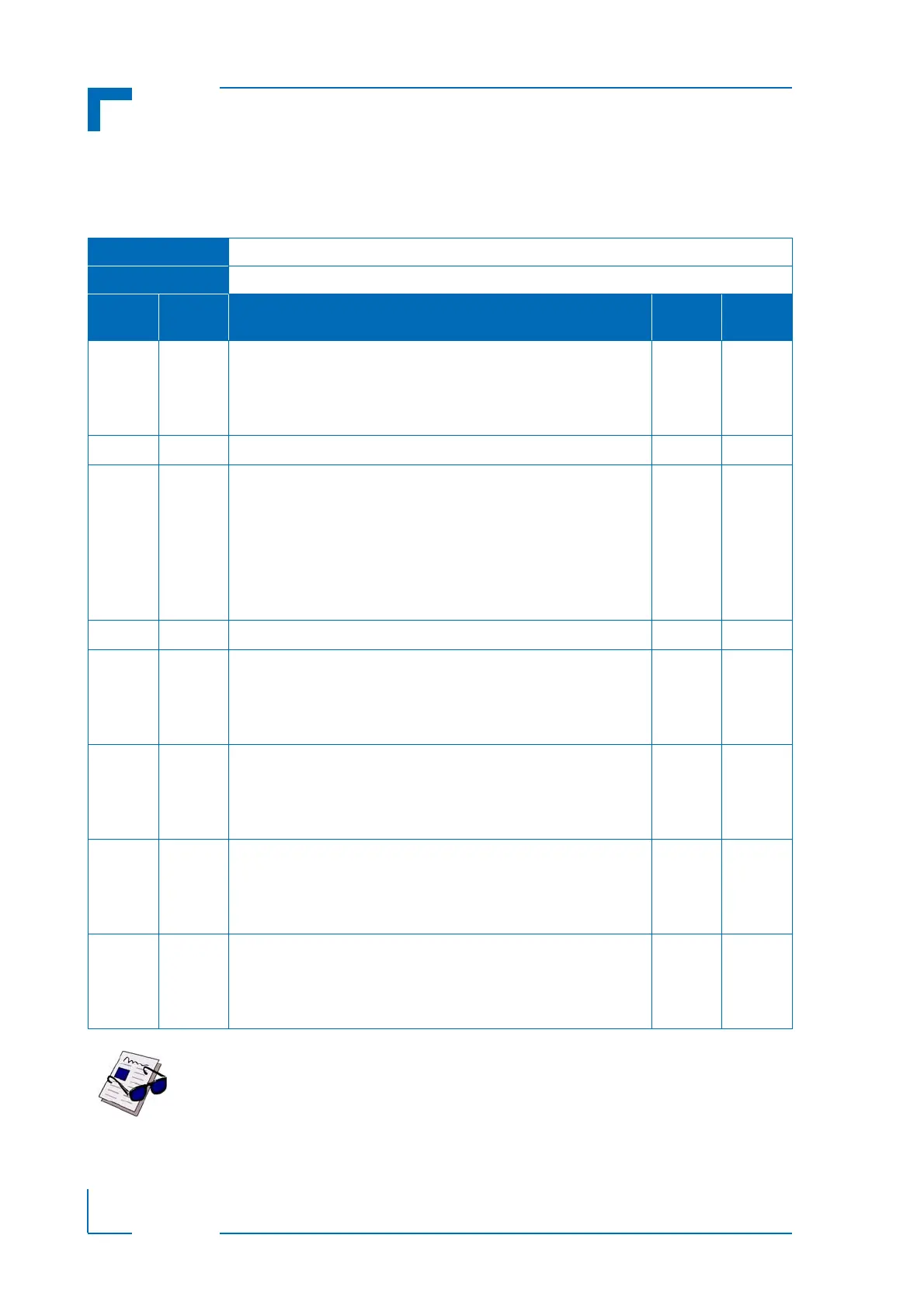

4.3.6 Reset Status Register (RSTAT)

The Reset Status Register is used to determine the host’s reset source.

Table 4-9: Reset Status Register (RSTAT)

REGISTER NAME RESET STATUS REGISTER (RSTAT)

ADDRESS 0x285

BIT NAME DESCRIPTION

RESET

VALUE

ACCESS

7 PORS Power-on reset status:

0 = System reset generated by software (warm reset)

1 = System reset generated by power-on (cold reset)

Writing a ’1’ to this bit clears the bit.

N/A R/W

6 Res. Reserved 0 R

5 SRST Software reset status:

0 = Reset is logged by SMC

1 = Reset is not logged by SMC

The uEFI BIOS/ software sets the bit to inform the SMC that the next

reset should not be logged.

Writing a ’1’ from the host to this bit sets the bit. After setting the bit,

it may be cleared via the SMC.

0R/W

4 Res. Reserved 0 R

3 IPRS SMC controller reset:

0 = System reset not generated by SMC

1 = System reset generated by SMC

Writing a ’1’ to this bit clears the bit.

0R/W

2 FPRS Front panel push button reset status (CP308-HDD):

0 = System reset not generated by front panel reset

1 = System reset generated by front panel reset

Writing a ’1’ to this bit clears the bit.

0R/W

1 CPRS CompactPCI reset status (PRST signal):

0 = System reset not generated by CPCI reset input

1 = System reset generated by CPCI reset input

Writing a ’1’ to this bit clears the bit.

0R/W

0 WTRS Watchdog timer reset status:

0 = System reset not generated by Watchdog timer

1 = System reset generated by Watchdog timer

Writing a ’1’ to this bit clears the bit.

0R/W

Note ...

The Reset Status Register is set to the default values by power-on reset, not by

PCI reset.

Loading...

Loading...