Reserved

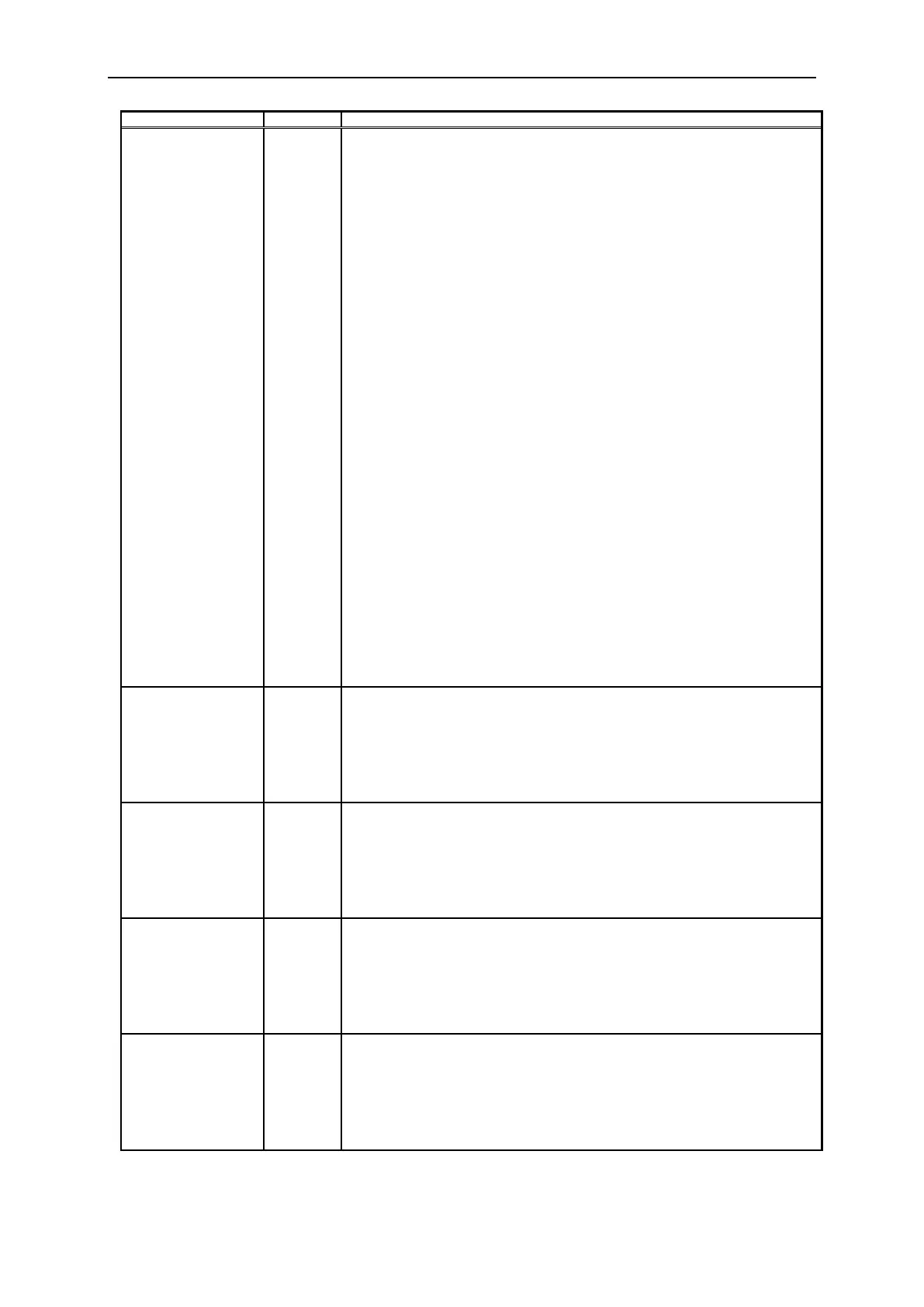

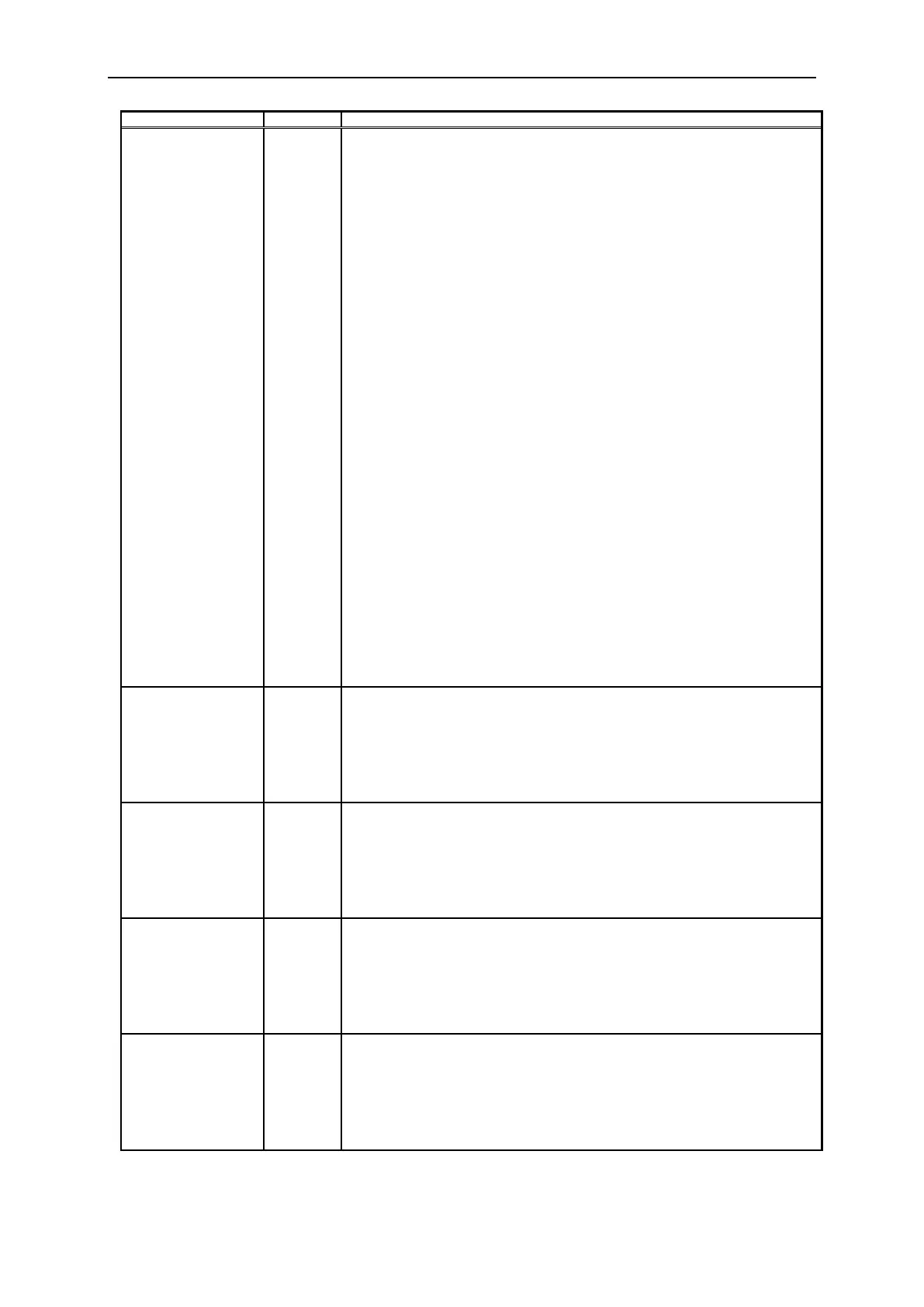

SPDUP_LDO_AFE: Short the noise filter resistor to speed up the settling time

0 – noise filter resistor in place (default)

1 – Noise filter resistor bypassed

should be connected to a 1~5uS at the power up

SPDUP_LDO_CPGN: Short the noise filter resistor to speed up the settling time

0 – noise filter resistor in place (default)

1 – Noise filter resistor bypassed

should be connected to a 1~5uS at the power up

SPDUP_LDO_CPSXR: Short the noise filter resistor to speed up the settling time

0 – noise filter resistor in place (default)

1 – Noise filter resistor bypassed

should be connected to a 1~5uS at the power up

SPDUP_LDO_CPSXT: Short the noise filter resistor to speed up the settling time

0 – noise filter resistor in place (default)

1 – Noise filter resistor bypassed

should be connected to a 1~5uS at the power up

SPDUP_LDO_DIG: Short the noise filter resistor to speed up the settling time

0 – noise filter resistor in place (default)

1 – Noise filter resistor bypassed

should be connected to a 1~5uS at the power up

SPDUP_LDO_DIGGN: Short the noise filter resistor to speed up the settling time

0 – noise filter resistor in place (default)

1 – Noise filter resistor bypassed

should be connected to a 1~5uS at the power up

SPDUP_LDO_DIGSXR: Short the noise filter resistor to speed up the settling time

0 – noise filter resistor in place (default)

1 – Noise filter resistor bypassed

should be connected to a 1~5uS at the power up

SPDUP_LDO_DIGSXT: Short the noise filter resistor to speed up the settling time

0 – noise filter resistor in place (default)

1 – Noise filter resistor bypassed

should be connected to a 1~5uS at the power up

SPDUP_LDO_DIVGN: Short the noise filter resistor to speed up the settling time

0 – noise filter resistor in place (default)

1 – Noise filter resistor bypassed

should be connected to a 1~5uS at the power up

Default: 00000000 00000000

Loading...

Loading...