HELIOS LED Processing Platform - USER GUIDE 45

Latency (Advanced) - (continued)

Key rules:

• Processor low latency is not compatible with GhostFrame MultiSource.

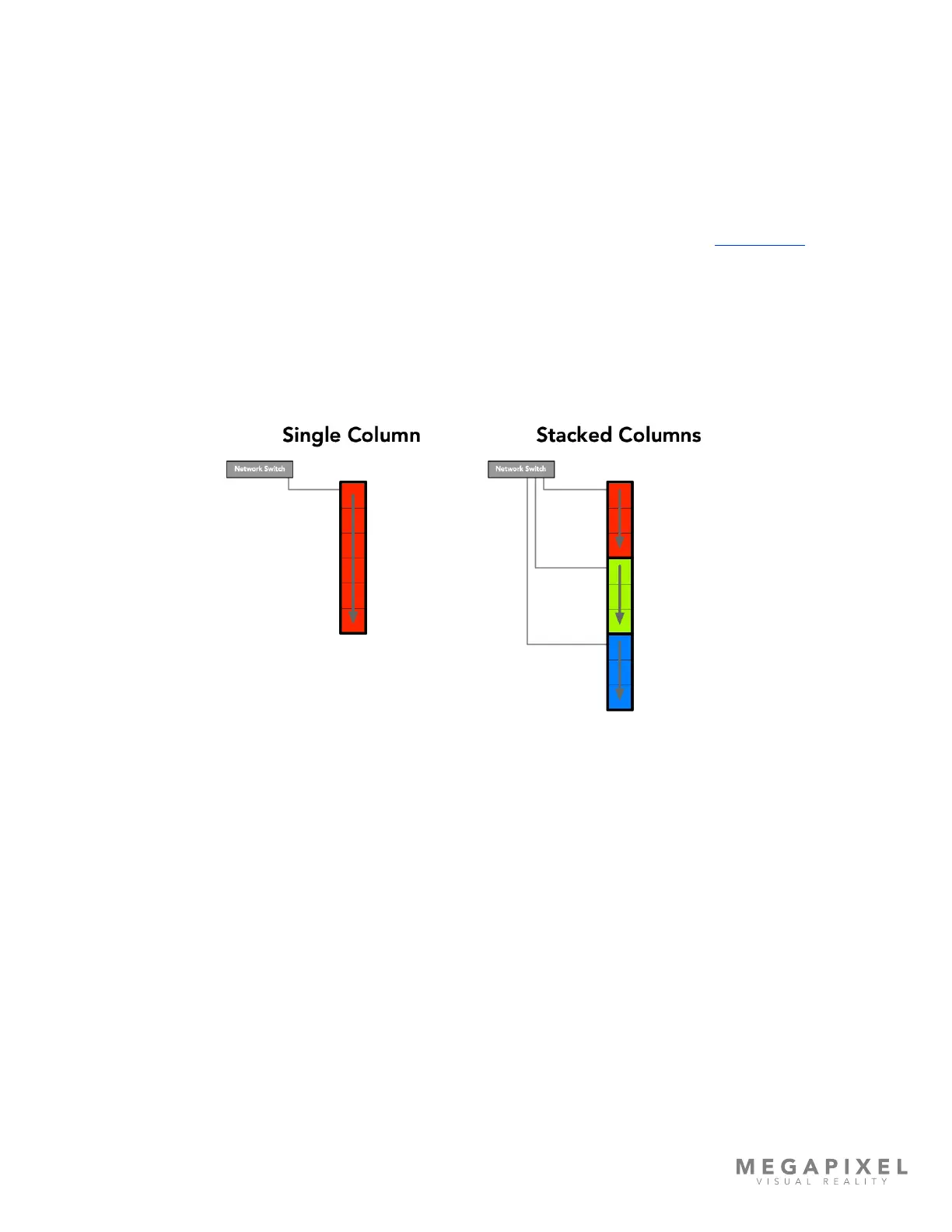

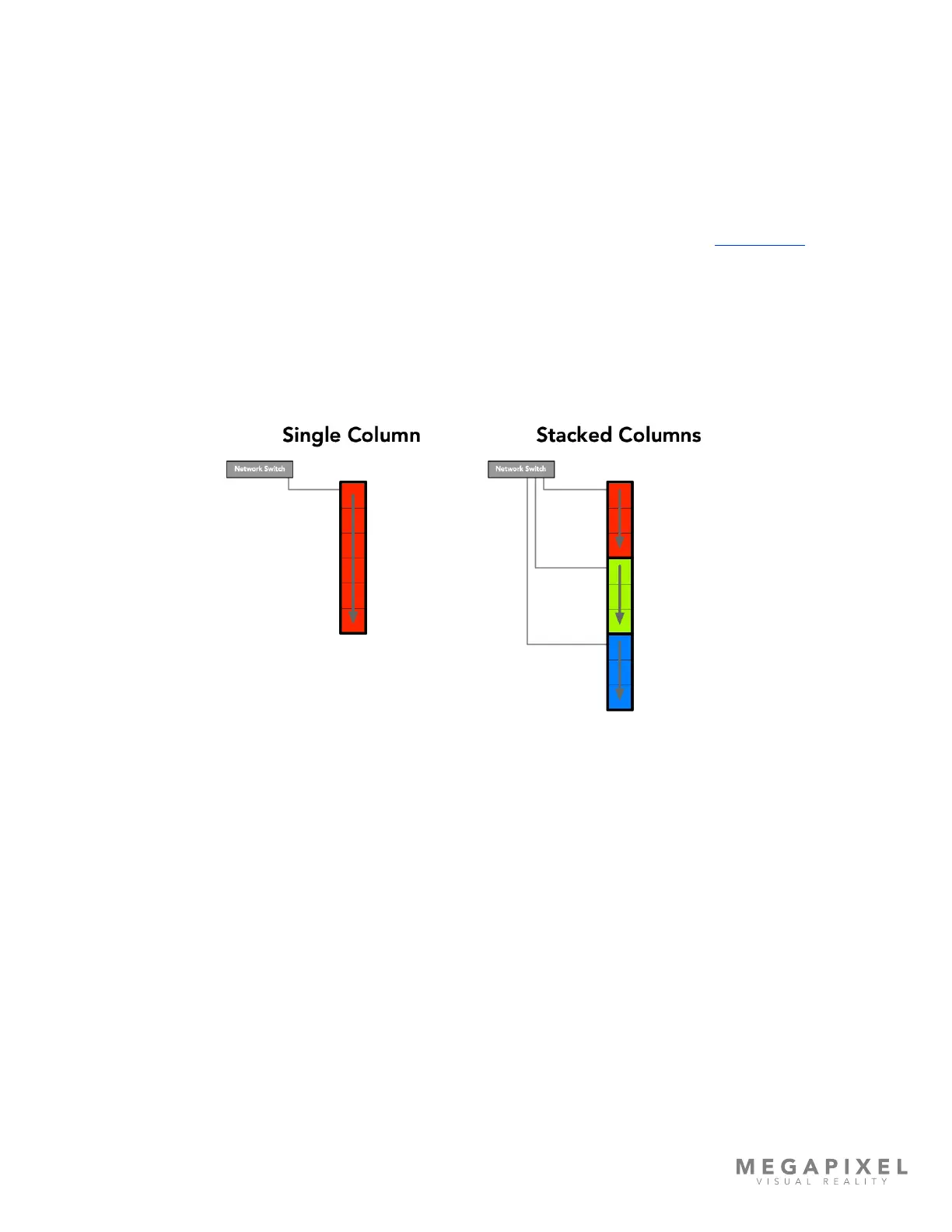

• Tile cabling and mapping must be in columns (top to bottom and bottom to top are both ok).

• There are no capacity limitations or reductions when tiles are cabled as a single column high. Therefore, tile quantity

per daisy chain is no different than normal (see the HELIOS Output Port Capacity section in Appendix G) for data

daisy chain limits). In the example below, the tile type has a maximum daisy chain of six (6) tiles. Although some tile

types can achieve larger daisy chains, this example is limited to six (6) for simplicity.

• Stacked columns (e.g. a wall that is taller than the maximum tile chain length) will have capacity reductions. The rule of

thumb is that when columns are stacked, the maximum string length is halved from that of normal operation. The

example tile type at normal operation has a maximum daisy chain of six (6). In a stacked conguration, the system

requires chains of three (3). Additionally, only the top ½ of the input may be used. For more specic design guidelines

contact MVR for assistance.

Figure 59: Single Column vs Stacked Columns

• Horizontal stitching of inputs is supported.

• Vertical stitching of inputs and Square Division are not supported.

Loading...

Loading...