R8C/20 Group, R8C/21 Group 14. Timers

Rev.2.00 Aug 27, 2008 Page 241 of 458

REJ09B0250-0200

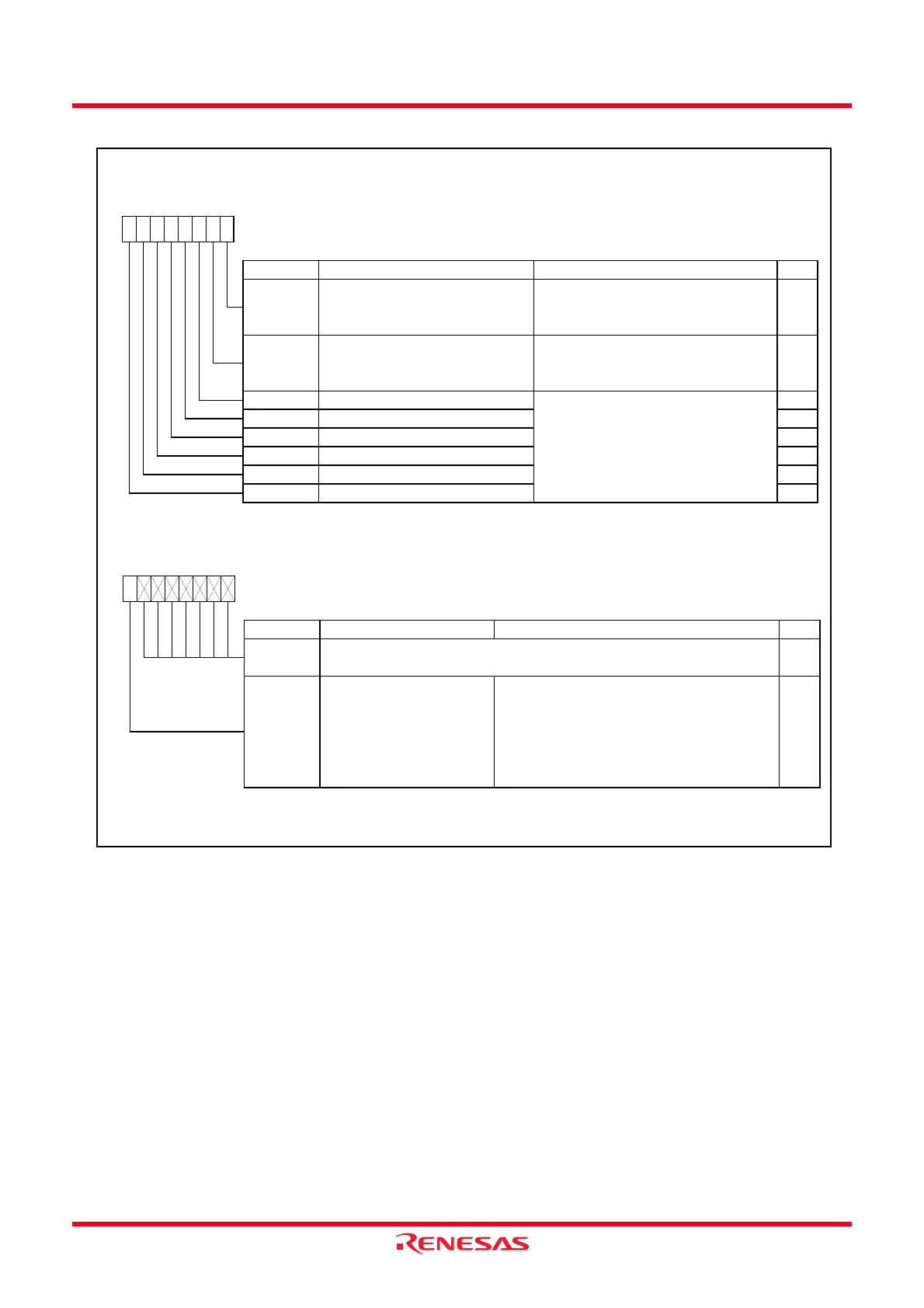

Figure 14.101 Registers TRDOER1 to TRDOER2 in PWM3 Mode

Timer RD Output Master Enable Register 1

Symbol Address After Reset

TRDOER1

013Bh FFh

Bit Symbol Bit Name Function RW

ED1 RW

EA 1

EB1 RW

TRDIOD1 output disable bit

TRDIOB1 output disable bit

EC1 TRDIOC1 output disable bit

TRDIOD0 output disable bit RW

TRDIOA1 output disable bit

RW

RW

Set these bits to 1 (programmable I/O port)

in PWM3 mode.

TRDIOC0 output disable bitEC0 RW

RW

EB0 RW

TRDIOA0 output disable bit 0 : Enable output

1 : Disable output (The TRDIOA0 pin is

used as a programmable I/O port.)

TRDIOB0 output disable bit 0 : Enable output

1 : Disable output (The TRDIOB0 pin is

used as a programmable I/O port.)

1111

b7 b6 b5 b4 b3 b2

ED0

b1 b0

11

EA 0

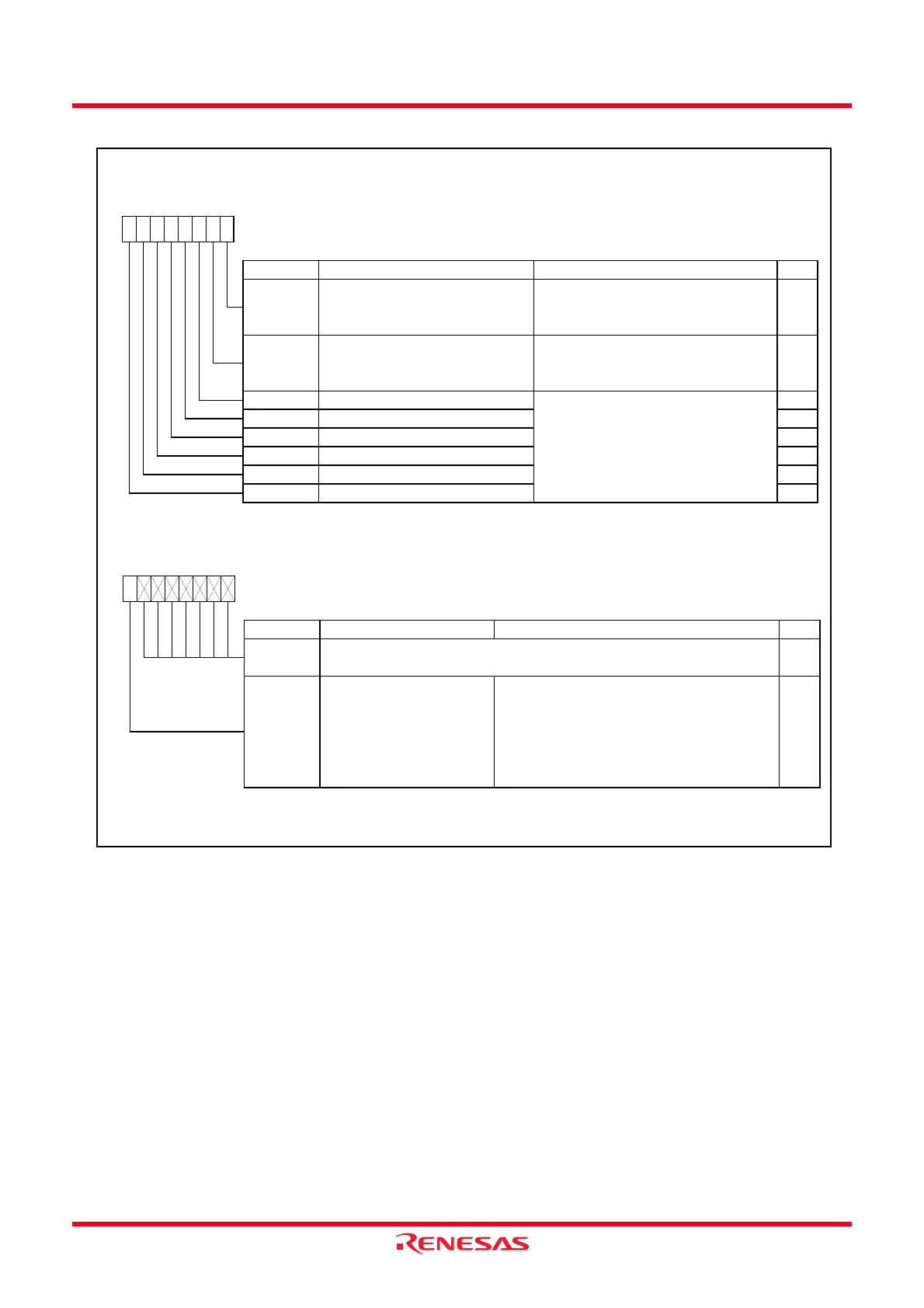

Timer RD Output Master Enable Register 2

Symbol Address After Reset

TRDOER2

013Ch 01111111b

Bit Symbol Bit Name Function RW

INT0

____

of pulse output forced 0 : Pulse output forced cutoff input disabled

1 : Pulse output forced cutoff input enabled

(All bits in the TRDOER1 register

are set to 1 (disable output) w hen “L” is

applied to the INT0

____

pin)

NOTE:

1. Refer to

14.3.4 Pulse Output Forced Cutoff

.

—

—

(b6 - b0)

Nothing is assigned. If necessary, set to 0.

When read, the content is 1.

RWPTO

cutoff signal input enabled

bit

(1)

b7 b6 b5 b4 b3 b2 b1 b0

Loading...

Loading...