STR-ZA1000ES/ZA2000ES/ZA3000ES

STR-ZA1000ES/ZA2000ES/ZA3000ES

4545

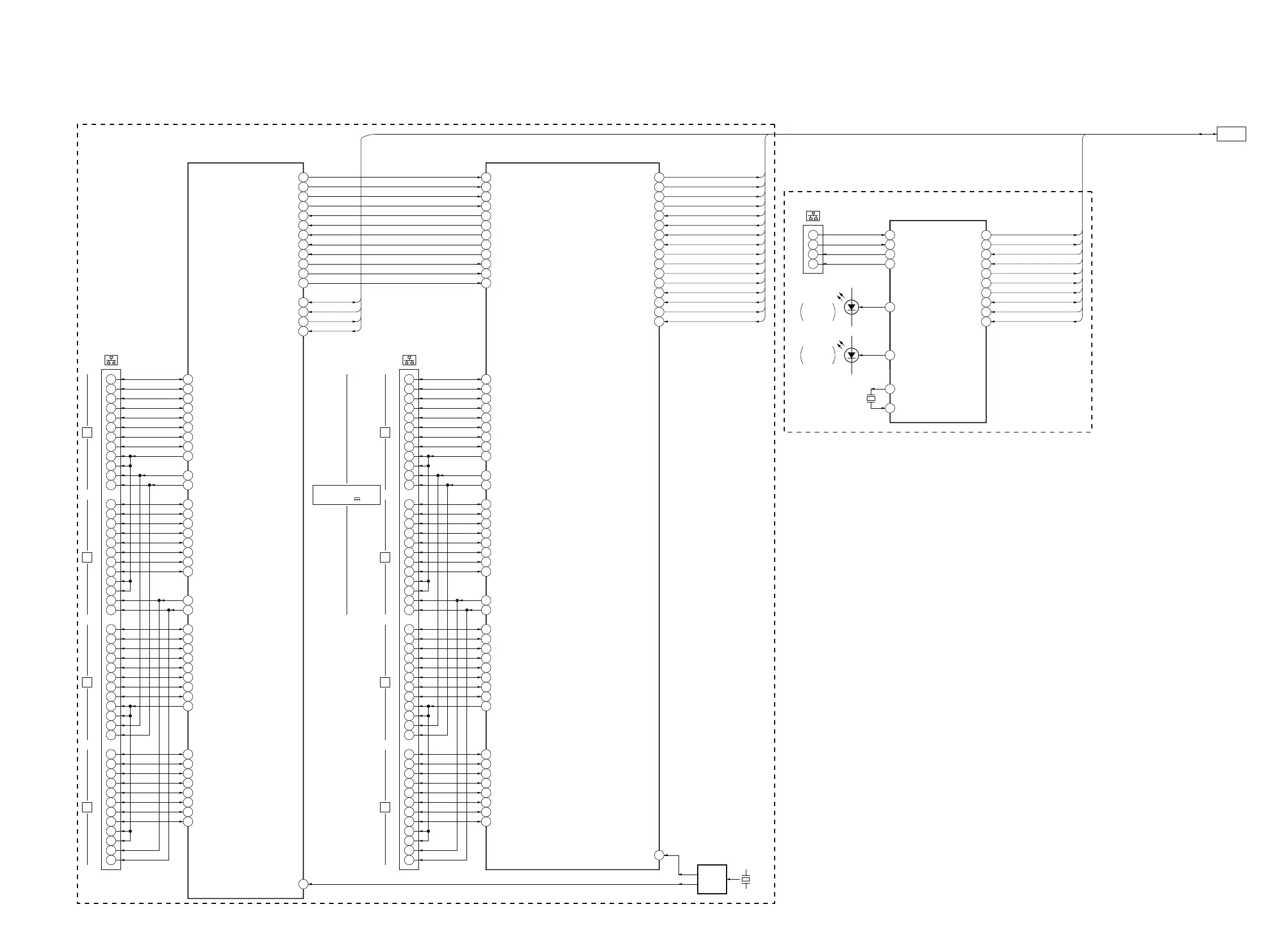

6-7. BLOCK DIAGRAM - NETWORK Section (1/2) -

11

10

4

5

3

2

8

9

17

19

18

20

22 P3_MDIP[0]

23 P3_MDIN[0]

25 P3_MDIP[1]

26 P3_MDIN[1]

27 P3_MDIP[2]

28 P3_MDIN[2]

29 P3_MDIP[3]

30 P3_MDIN[3]

34 R1_LED/P1_LED0/LED_SEL[0]

40 EE_DOUT/C3_LED/P5_LED0

38 EE_CLK/C1_LED/FLOW

J7000

PoE

EACH DC 48V 15.4W

31

30

24

25

23

22

28

29

37

39

38

40

13 P2_MDIP[0]

14 P2_MDIN[0]

16 P2_MDIP[1]

17 P2_MDIN[1]

18 P2_MDIP[2]

19 P2_MDIN[2]

20 P2_MDIP[3]

21 P2_MDIN[3]

39 EE_CS/C2_LED/P4_LED0/S_SEL

36 EE_DIN/C0_LED/P3_LED0/EEE_WP

51

50

44

45

43

42

48

49

57

59

58

60

4 P1_MDIP[0]

5 P1_MDIN[0]

7 P1_MDIP[1]

8 P1_MDIN[1]

9 P1_MDIP[2]

10 P1_MDIN[2]

11 P1_MDIP[3]

12 P1_MDIN[3]

33 R0_LED/P0_LED0/LED_SEL[0]

71

70

64

65

63

62

68

69

77

79

78

80

113 P0_MDIP[0]

114 P0_MDIN[0]

116 P0_MDIP[1]

117 P0_MDIN[1]

119 P0_MDIP[2]

120 P0_MDIN[2]

121 P0_MDIP[3]

122 P0_MDIN[3]

ETHERNET INTERFACE

IC7000

3

6

1

2

J8750

1

2

3

4

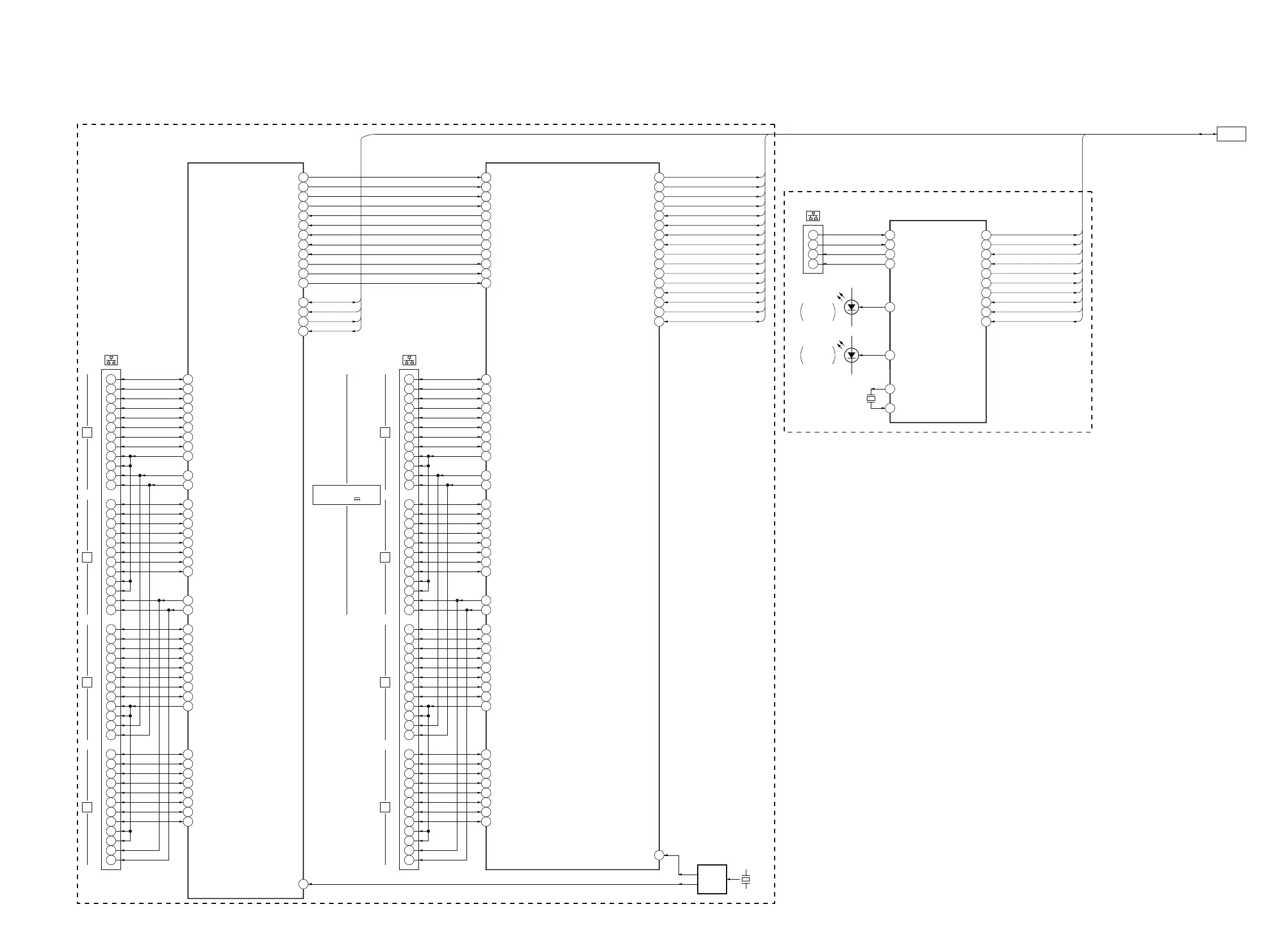

22 P3_MDIP[0]

23 P3_MDIN[0]

25 P3_MDIP[1]

26 P3_MDIN[1]

27 P3_MDIP[2]

28 P3_MDIN[2]

29 P3_MDIP[3]

30 P3_MDIN[3]

34 R1_LED/P1_LED0/LED_SEL[0]

40 EE_DOUT/C3_LED/P5_LED0

38 EE_CLK/C1_LED/FLOW

13 P2_MDIP[0]

14 P2_MDIN[0]

16 P2_MDIP[1]

17 P2_MDIN[1]

18 P2_MDIP[2]

19 P2_MDIN[2]

20 P2_MDIP[3]

21 P2_MDIN[3]

39 EE_CS/C2_LED/P4_LED0/S_SEL

36 EE_DIN/C0_LED/P3_LED0/EEE_WP

4 P1_MDIP[0]

5 P1_MDIN[0]

7 P1_MDIP[1]

8 P1_MDIN[1]

9 P1_MDIP[2]

10 P1_MDIN[2]

11 P1_MDIP[3]

12 P1_MDIN[3]

33 R0_LED/P0_LED0/LED_SEL[0]

93P6_OUTD[0]/P6_MODE[0]

92P6_OUTD[1]/P6_MODE[1]

91P6_OUTD[2]/P6_MODE[2]

90P6_OUTD[3]/P6_VDDOS[1]

101P6_IND[0]

102P6_IND[1]

103P6_IND[2]

104P6_IND[3]

100P6_INDV

98P6_INCLK

95P6_OUTCLK/P6_TXC

94P6_OUTEN/P6_VDDOS[0]

113 P0_MDIP[0]

114 P0_MDIN[0]

116 P0_MDIP[1]

117 P0_MDIN[1]

119 P0_MDIP[2]

120 P0_MDIN[2]

121 P0_MDIP[3]

122 P0_MDIN[3]

ETHERNET INTERFACE

IC7250

5

6

7

8

75

76

77

78

69

68

67

66

70

71

72

P5_IND[0]/GPIO[11]

101P6_IND[0]

ETHEPHY_HUB1_RESET

P6_RXD0

102P6_IND[1]

P6_RXD1

103P6_IND[2]

P6_RXD2

104P6_IND[3]

P6_RXD3

93P6_OUTD[0]/P6_MODE[0]

P6_OUTD[0]

92P6_OUTD[1]/P6_MODE[1]

P6_OUTD[1]

91P6_OUTD[2]/P6_MODE[2]

P6_OUTD[2]

90P6_OUTD[3]/P6_VDDOS[1]

P6_OUTD[3]

94P6_OUTEN/P6_VDDOS[0]

P6_OUTEN

95P6_OUTCLK/P6_TXC

P6_OUTCLK

98P6_INCLK

P6_RXCLK

100P6_INDV

P6_RXDV

60MDIO_CPU

MDIO_CPU

61MDC_CPU

MDC_CPU

31RESETN

HUB2_RESET

60MDIO_CPU

MDIO_CPU

61MDC_CPU

MDC_CPU

31RESETN

126XTAL_IN

P5_IND[1]/GPIO[10]

P5_IND[2]/GPIO[9]

P5_IND[3]/GPIO[8]

P5_OUTD[0]/P5_MODE[0]

P5_OUTD[1]/P5_MODE[1]

P5_OUTD[2]/P5_MODE[2]

P5_OUTD[3]/P5_VDDOS[1]

P5_OUTEN/P5_VDDOS[0]

P5_OUTCLK/P5_TXC/GPIO[14]

P5_INCLK/GPIO[13]

74 P5_INDV/GPIO[12]

ETHERNET INTERFACE

IC8750

5

6

3

4

MDI+[1]

12TXD[0]

P6_RXD0

13TXD[1]

P6_RXD1

8RXD[0]/CLK_CTL

P6_OUTD[0]

9RXD[1]

P6_OUTD[1]

20CRS_DV

P6_OUTEN

11REF_CLK

P6_OUTCLK

14TXEN

P6_RXDV

17MDIO

MDIO_CPU

16MDC

MDC_CPU

15PHYRSTB

ETHEPHY_HUB1_RESET

MDI–[1]

MDI+[0]

MDI–[0]

>016B

P6_OUTD[0] – P6_OUTD[3], P6_RXD0 – P6_RXD3,

P6_OUTEN, P6_OUTCLK, P6_RXCLK, P6_RXDV,

MDIO_CPU, MDC_CPU, ETHEPHY_HUB1_INT,

HUB2_INT, ETHEPHY_HUB1_RESET, HUB2_RESET

CLOCK

BUFFER

IC7006

X7002

25MHz

126XTAL_IN

RX+

RX–

TX+

TX–

18

LED0/PHYAD[0]/

PMEB/INTB

19 LED1/PHYAD[1]

CKXTAL2

24

CKXTAL1

25

X8750

25MHz

42INTN

ETHEPHY_HUB1_INT

42INTN

HUB2_INT

11

10

4

5

3

2

8

9

17

19

18

20

31

30

24

25

23

22

28

29

37

39

38

40

51

50

44

45

43

42

48

49

57

59

58

60

71

70

64

65

63

62

68

69

77

79

78

80

ACTIVE

INDICATOR

D8751

ACTIVE

INDICATOR

D8750

(ZA3000ES)

(ZA1000ES/ZA2000ES)

J7250

(Page 46)

Ver. 1.1

Loading...

Loading...